# Syllabus of UNDERGRADUATE DEGREE COURSE

# **Electronics & Communication Engineering**

# Rajasthan Technical University, Kota Effective from session: 2018 – 2019

**SYLLABUS**

II Year - III Semester: B.Tech. (Electronics & Communication Engineering)

### **3EC2-01: Advance Engineering Mathematics-I**

Max Marks: 150 (IA:30 ETE:120)

3 Credits

|    | redits Max. Marks: 150 (IA:30, E'<br>OT:OP End Term Exam: 3                                                                                                                                                                                                                                                                                                                                                                                   | •     |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| SN | Contents                                                                                                                                                                                                                                                                                                                                                                                                                                      | Hours |

| 1  | Numerical Methods – 1:<br>Finite differences, Relation between operators, Interpolation using<br>Newton's forward and backward difference formulae. Gauss's<br>forward and backward interpolation formulae. Stirling's Formulae.<br>Interpolation with unequal intervals: Newton's divided difference<br>and Lagrange's formulae.<br>Numerical Differentiation, Numerical integration: Trapezoidal rule<br>and Simpson's 1/3rd and 3/8 rules. | 10    |

| 2  | Numerical Methods – 2:<br>Numerical solution of ordinary differential equations: Taylor's<br>series, Euler and modified Euler's methods. Runge- Kutta method<br>of fourth order for solving first and second order equations. Milne's<br>and Adam's predicator-corrector methods.<br>Solution of polynomial and transcendental equations-Bisection<br>method, Newton-Raphson method and Regula-Falsi method.                                  | 8     |

| 3  | Laplace Transform:<br>Definition and existence of Laplace transform, Properties of Laplace<br>Transform and formulae, Unit Step function, Dirac Delta function,<br>Heaviside function, Laplace transform of periodic functions.<br>Finding inverse Laplace transform by different methods,<br>convolution theorem. Evaluation of integrals by Laplace transform,<br>solving ODEs by Laplace transforms method.                                | 10    |

| 4  | <b>Fourier Transform:</b><br>Fourier Complex, Sine and Cosine transform, properties and formulae, inverse Fourier transforms, Convolution theorem, application of Fourier transforms to partial ordinary differential equation (One dimensional heat and wave equations only).                                                                                                                                                                | 7     |

| 5  | <b>Z-Transform:</b><br>Definition, properties and formulae, Convolution theorem, inverse<br>Z-transform, application of Z-transform to difference equation.                                                                                                                                                                                                                                                                                   | 5     |

|    | Total                                                                                                                                                                                                                                                                                                                                                                                                                                         | 40    |

II Year - III Semester: B.Tech. (Electronics & Communication Engineering)

#### 3EC1-02/4EC1-02: Technical Communication

#### 2 Credit 2L:0T:0P

### Max. Marks: 100 (IA:20, ETE:80) End Term Exam: 2 Hours

| SN | Contents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Hours |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 1  | <b>Introduction to Technical Communication-</b> Definition of technical communication, Aspects of technical communication, forms of technical communication, importance of technical communication, technical communication skills (Listening, speaking, writing, reading writing), linguistic ability, style in technical communication.                                                                                                                                                               | 4     |

| 2  | <b>Comprehension of Technical Materials/Texts and</b><br><b>Information Design &amp; development-</b> Reading of technical<br>texts, Readingand comprehending instructions and technical<br>manuals, Interpreting and summarizing technical texts, Note-<br>making. Introduction of different kinds of technical documents,<br>Information collection, factors affecting information and<br>document design, Strategies for organization, Information design<br>and writing for print and online media. | 6     |

| 3  | <b>Technical Writing, Grammar and Editing</b> - Technical writing<br>process, forms of technical discourse, Writing, drafts and<br>revising, Basics of grammar, common error in writing and<br>speaking, Study of advanced grammar, Editing strategies to<br>achieve appropriate technical style, Introduction to advanced<br>technical communication. Planning, drafting and writing Official<br>Notes, Letters, E-mail, Resume, Job Application, Minutes of<br>Meetings.                              | 8     |

| 4  | <b>Advanced Technical Writing</b> - Technical Reports, types of technical reports, Characteristics and formats and structure of technical reports. Technical Project Proposals, types of technical proposals, Characteristics and formats and structure of technical proposals. Technical Articles, types of technical articles, Writing strategies, structure and formats of technical articles.                                                                                                       | 8     |

|    | Total                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 26    |

SYLLABUS

II Year - III Semester: B.Tech. (Electronics & Communication Engineering)

#### 3EC1-03/4EC1-03: Managerial Economics And Financial Accounting 2 Credit Max. Marks: 100 (IA:20, ETE:80) 2L:0T:0P End Term Exam: 2 Hours

|    | DT:OP End Term Exam:                                                                                                                                                                                                                                                                                                                                                                             |       |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| SN | Contents                                                                                                                                                                                                                                                                                                                                                                                         | Hours |

| 1  | Basic economic concepts-<br>Meaning, nature and scope of economics, deductive vs inductive<br>methods, static and dynamics, Economic problems: scarcity and<br>choice, circular flow of economic activity, national income-concepts<br>and measurement.                                                                                                                                          | 4     |

| 2  | Demand and Supply analysis-<br>Demand-types of demand, determinants of demand, demand<br>function, elasticity of demand, demand forecasting –purpose,<br>determinants and methods, Supply-determinants of supply, supply<br>function, elasticity of supply.                                                                                                                                      | 5     |

| 3  | Production and Cost analysis-<br>Theory of production- production function, law of variable<br>proportions, laws of returns to scale, production optimization, least<br>cost combination of inputs, isoquants. Cost concepts-explicit and<br>implicit cost, fixed and variable cost, opportunity cost, sunk costs,<br>cost function, cost curves, cost and output decisions, cost<br>estimation. | 5     |

| 4  | Market structure and pricing theory-<br>Perfect competition, Monopoly, Monopolistic competition,<br>Oligopoly.                                                                                                                                                                                                                                                                                   | 4     |

| 5  | Financial statement analysis-<br>Balance sheet and related concepts, profit and loss statement and<br>related concepts, financial ratio analysis, cash-flow analysis,<br>funds-flow analysis, comparative financial statement, analysis and<br>interpretation of financial statements, capital budgeting<br>techniques.                                                                          | 8     |

|    | Total                                                                                                                                                                                                                                                                                                                                                                                            | 26    |

**SYLLABUS**

II Year - III Semester: B.Tech. (Electronics & Communication Engineering)

#### **3EC4-04: Digital System Design**

#### 3 Credits 3L:0T:0P

#### Max. Marks: 150 (IA:30, ETE:120) End Term Exam: 3 Hours

| SN | Contents                                                                                                                                                                                                                                                                                                                                                                      | Hours |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 1  | Logic Simplification and Combinational Logic Design: Review of<br>Boolean Algebra and De Morgan's Theorem, SOP & POS forms,<br>Canonical forms, Karnaugh maps up to 6 variables, Binary codes,<br>Code Conversion.                                                                                                                                                            | 7     |

| 2  | MSI devices like Comparators, Multiplexers, Encoder, Decoder,<br>Driver & Multiplexed Display, Half and Full Adders, Subtractors,<br>Serial and Parallel Adders, BCD Adder, Barrel shifter and ALU                                                                                                                                                                            | 8     |

| 3  | Sequential Logic Design: Building blocks like S-R, JK and Master-<br>Slave JK FF, Edge triggered FF, Ripple and Synchronous counters,<br>Shift registers, Finite state machines, Design of Synchronous FSM,<br>Algorithmic State Machines charts. Designing synchronous circuits<br>like Pulse train generator, Pseudo Random Binary Sequence<br>generator, Clock generation. | 9     |

| 4  | Logic Families and Semiconductor Memories: TTL NAND gate,<br>Specifications, Noise margin, Propagation delay, fan-in, fan-out,<br>Tristate TTL, ECL, CMOS families and their interfacing, memory<br>elements, Concept of Programmable logic devices like FPGA. Logic<br>implementation using programmable devices.                                                            | 8     |

| 5  | VLSI Design flow: Design entry: Schematic, FSM & HDL, different<br>modeling styles in VHDL, Data types and objects, Dataflow,<br>Behavioral and Structural Modeling, Synthesis and Simulation<br>VHDL constructs and codes for combinational and sequential<br>circuits.                                                                                                      | 8     |

|    | Total                                                                                                                                                                                                                                                                                                                                                                         | 40    |

II Year - III Semester: B.Tech. (Electronics & Communication Engineering)

#### **Course Outcome:**

| Course<br>Code | Course<br>Name        | Course<br>Outco<br>me | Details                                                                                                                                                                      |

|----------------|-----------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                |                       | CO 1                  | Develop the understanding of number system<br>and its application in digital electronics.                                                                                    |

|                | ця                    | CO 2                  | Development and analysis of K-map to solve<br>the Boolean function to the simplest form for<br>the implementation of compact digital<br>circuits.                            |

| 3EC4-04        | Digital System Design | CO 3                  | Design various combinational and sequential<br>circuits using various metrics: switching<br>speed, throughput/latency, gate count and<br>area, energy dissipation and power. |

| 31             | Digital S             | CO 4                  | Understanding Interfacing between digital<br>circuits and analog component using Analog<br>to Digital Converter (ADC), Digital to Analog<br>Converter (DAC) etc.             |

|                |                       | CO 5                  | Design and implement semiconductor<br>memories, programmable logic devices (PLDs)<br>and field programmable gate arrays (FPGA) in<br>digital electronics.                    |

#### **CO-PO Mapping:**

| Subject                             | Course<br>Outcome<br>s | <b>PO</b><br>1 | PO<br>2 | PO<br>3 | PO<br>4 | PO<br>5 | PO<br>6 | PO<br>7 | PO<br>8 | PO<br>9 | PO<br>10 | PO<br>11           | PO<br>12 |

|-------------------------------------|------------------------|----------------|---------|---------|---------|---------|---------|---------|---------|---------|----------|--------------------|----------|

| В                                   | CO 1                   | 3              | 2       | 2       | 1       |         | 1       |         |         |         |          |                    |          |

| 04<br>7stei<br>n                    | CO 2                   | 3              | 2       | 3       | 2       |         |         |         |         |         |          |                    |          |

| 3EC4-04<br>gital Syst<br>Design     | CO 3                   | 2              | 2       | 3       | 1       | 1       |         |         |         |         |          |                    |          |

| 3EC4-04<br>Digital System<br>Design | CO 4                   | 3              | 2       | 1       | 1       | 1       |         |         |         |         |          |                    |          |

|                                     | CO 5                   | 2              | 1       | 3       | 1       | 1       |         |         |         |         |          |                    |          |

|                                     | 3: \$                  | Strong         | gly     | 2       | 2: Mo   | derat   | te      |         |         |         | of Dean  | Acader<br>ical Uni |          |

#### Lecture Plan:

| Lecture<br>No. | Content to be taught                                                                                                 |

|----------------|----------------------------------------------------------------------------------------------------------------------|

| Lecture 1      | Zero Lecture                                                                                                         |

| Lecture 2      | Review of Boolean Algebra                                                                                            |

| Lecture 3      | DeMorgan's Theorem, SOP & POS forms,                                                                                 |

| Lecture 4      | Problem of SOP and POS forms of boolean functions.                                                                   |

| Lecture 5      | Simplification of karnaugh map up to 6 variables                                                                     |

| Lecture 6      | Simplification of karnaugh map up to 6 variables                                                                     |

| Lecture 7      | Simplification of karnaugh map up to 6 variables                                                                     |

| Lecture 8      | Binary codes and code conversion                                                                                     |

| Lecture 9      | Binary codes and code conversion                                                                                     |

| Lecture 10     | Encoder, Decoder                                                                                                     |

| Lecture 11     | Half and Full Adders, Subtractors, Serial and Parallel Adders                                                        |

| Lecture 12     | BCD Adder, Barrel shifter                                                                                            |

| Lecture 13     | S-R FF, edge triggered and level triggered                                                                           |

| Lecture 14     | D and J-K FF                                                                                                         |

| Lecture 15     | Master-Slave JK FF and T FF                                                                                          |

| Lecture 16     | Ripple and Synchronous counters                                                                                      |

| Lecture 17     | Other type of counters                                                                                               |

| Lecture 18     | Shift registers, Finite state machines, Asynchronous FSM                                                             |

| Lecture 19     | Design of synchronous FSM                                                                                            |

| Lecture 20     | Design of synchronous FSM                                                                                            |

| Lecture 21     | Design of synchronous FSM                                                                                            |

| Lecture 22     | Designing synchronous circuits (pulse train generator, pseudo<br>random binary sequence generator, clock generation) |

II Year - III Semester: B.Tech. (Electronics & Communication Engineering)

| Lecture 23 | TTL NAND gate, specifications, noise margin, propagation delay,                |

|------------|--------------------------------------------------------------------------------|

|            | fan-in, fan-out                                                                |

| Lecture 24 | TTL NAND gate                                                                  |

| Lecture 25 | Tristate TTL, ECL                                                              |

| Lecture 26 | CMOS families and their interfacing                                            |

| Lecture 27 | CMOS families and their interfacing                                            |

| Lecture 28 | Read-Only Memory, Random Access Memory                                         |

| Lecture 29 | Programmable Logic Arrays (PLA)                                                |

| Lecture 30 | Programmable Array Logic (PAL),                                                |

| Lecture 31 | Field Programmable Gate Array (FPGA)                                           |

| Lecture 32 | Combinational PLD-Based State Machines,                                        |

| Lecture 33 | State Machines on a Chip                                                       |

| Lecture 34 | Schematic, FSM & HDL                                                           |

| Lecture 35 | Different modeling styles in VHDL                                              |

| Lecture 36 | Data types and objects, Data flow                                              |

| Lecture 37 | Behavioral and Structural Modeling                                             |

| Lecture 38 | Behavioral and Structural Modeling                                             |

| Lecture 39 | Simulation VHDL constructs and codes for combinational and sequential circuits |

| Lecture 40 | Simulation VHDL constructs and codes for combinational and sequential circuits |

#### Content delivery method:

- 1. Chalk and Duster

- **2.** PPT

- 3. Hand-outs

II Year - III Semester: B.Tech. (Electronics & Communication Engineering)

### Sample Assignments:

| Assignment 1 | <ul> <li>Q1.Using K-maps, find the minimal Boolean expression of the following SOP and POS representations.</li> <li>a. f (w,x,y,z) = Σ (7,13,14,15)</li> <li>b. f(w,x,y,z) = Σ (1,3,4,6,9,11,14,15)</li> <li>c. f(w,x,y,z) = Π(1,4,5,6,11,12,13,14,15)</li> <li>d. f(w,x,y,z) = Σ (1,3,4,5,7,8,9,11,15)</li> <li>e. f(w,x,y,z) = Π (0,4,5,7,8,9,13,15)</li> <li>Q2. Find the function h(a,b,c,d) such that f = f<sup>d</sup>.</li> </ul> |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              | f (a,b,c,d) = $a \cdot b \cdot c + (a \cdot c + b) \cdot d + h(a,b,c,d)$<br><b>Q3.</b> Using K-maps of the functions f1 and f2, find the                                                                                                                                                                                                                                                                                                  |

|              | following: (provide                                                                                                                                                                                                                                                                                                                                                                                                                       |

|              | the canonical form expression and simplify)                                                                                                                                                                                                                                                                                                                                                                                               |

|              | a. T1 = f1 $\cdot$ f2                                                                                                                                                                                                                                                                                                                                                                                                                     |

|              | b. $T2 = f1 + f2$                                                                                                                                                                                                                                                                                                                                                                                                                         |

|              | c. T3 = f1 $\oplus$ f2                                                                                                                                                                                                                                                                                                                                                                                                                    |

|              | where f1(w,x,y,z) = $\Sigma$ (0,2,4,9,12,15), f2(w,x,y,z) = $\Sigma$ (1,2,4,5,12,13)                                                                                                                                                                                                                                                                                                                                                      |

| Assignment 2 | <b>Q1</b> . Draw the state diagram of a serial adder.                                                                                                                                                                                                                                                                                                                                                                                     |

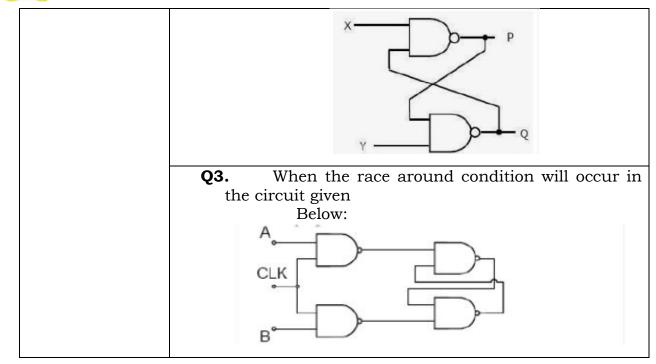

|              | <b>Q2.</b> In the following circuit, given binary values were applied to the                                                                                                                                                                                                                                                                                                                                                              |

|              | Inputs X and Y inputs of the NAND latch shown<br>in the figure. X =                                                                                                                                                                                                                                                                                                                                                                       |

|              | 0, Y = 1; X = 0, Y = 0; X = 1, Y = 1. Find out the corresponding stable output P, Q.                                                                                                                                                                                                                                                                                                                                                      |

II Year - III Semester: B.Tech. (Electronics & Communication Engineering)

**SYLLABUS**

II Year - III Semester: B.Tech. (Electronics & Communication Engineering)

#### 3EC4-05: Signals & Systems

#### 3 Credits 3L:0T:0P

#### Max. Marks: 150 (IA:30, ETE:120) End Term Exam: 3 Hours

#### SN **Contents** Hours 1 Energy and power signals, continuous and discrete time signals, continuous and discrete amplitude signals. System properties: 6 linearity: additivity and homogeneity, shift-invariance, causality, stability, realizability. Linear shift-invariant (LSI) systems, impulse response and step 2 response, convolution, input output behavior with aperiodic convergent inputs. Characterization of causality and stability of 7 linear shift-invariant systems. System representation through differential equations and difference equations Periodic and semi-periodic inputs to an LSI system, the notion of 3 a frequency response and its relation to the impulse response, representation, Fourier Fourier series the Transform. convolution/multiplication and their effect in the frequency 8 domain, magnitude and phase response, Fourier domain duality. The Discrete-Time Fourier Transform (DTFT) and the Discrete Fourier Transform (DFT). Parseval's Theorem. The idea of signal space and orthogonal bases The Laplace Transform, notion of eigen functions of LSI systems, a 4 basis of eigen functions, region of convergence, poles and zeros of 6 system, Laplace domain analysis, solution to differential equations and system behavior. The z-Transform for discrete time signals and systems- eigen 5 5 functions, region of convergence, z-domain analysis. State-space analysis and multi-input, multi-output 6 representation. The state-transition matrix and its role. The Sampling Theorem and its implications- Spectra of sampled 8 signals. Reconstruction: ideal interpolator, zero-order hold, firstorder hold, and so on. Aliasing and its effects. Relation between continuous and discrete time systems. Total 40

II Year - III Semester: B.Tech. (Electronics & Communication Engineering) Course Outcome:

| Course<br>Code | Course<br>Name       | Course<br>Outcom<br>e                 | Details                                                                                                 |  |  |  |  |  |

|----------------|----------------------|---------------------------------------|---------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|                |                      | CO 1                                  | Analyze different types of signals and system properties                                                |  |  |  |  |  |

| 3EC4-05        | Signals &<br>Systems | CO 2                                  | Represent continuous and discrete systems in<br>time and frequency domain using different<br>transforms |  |  |  |  |  |

| E<br>B         | Sig                  | CO 3                                  | Investigate whether the system is stable.                                                               |  |  |  |  |  |

|                | ~                    | CO 4                                  | Sampling and reconstruction of a signal.                                                                |  |  |  |  |  |

|                |                      | CO 5 Acquire an understanding of MIMO |                                                                                                         |  |  |  |  |  |

### **CO-PO Mapping:**

| Subject       | Course<br>Outcome<br>s | <b>PO</b><br>1 | PO<br>2 | PO<br>3 | PO<br>4 | PO<br>5 | PO<br>6 | PO<br>7 | PO<br>8 | PO<br>9 | PO<br>10 | PO<br>11 | PO<br>12 |

|---------------|------------------------|----------------|---------|---------|---------|---------|---------|---------|---------|---------|----------|----------|----------|

| ms            | CO 1                   | 3              | 3       | 1       | 2       | 2       |         |         | 1       |         |          |          | 2        |

| 05<br>Systems | CO 2                   | 3              | 1       |         | 2       | 3       |         |         | 1       |         |          |          | 2        |

| န် နို        | CO 3                   | 3              | 2       | 2       | 3       |         |         |         |         |         |          |          | 2        |

| - 60          | CO 4                   | 3              | 2       | 3       | 3       | 1       |         |         |         |         |          |          |          |

| Sign          | CO 5                   | 3              | 2       | 2       | 3       | 1       |         |         | 2       |         |          |          | 1        |

|               | 3:                     |                | 2: Mo   | odera   | te      |         |         | 1: We   | eak     |         |          |          |          |

II Year - III Semester: B.Tech. (Electronics & Communication Engineering)

#### Lecture Plan:

| Lecture<br>No. | Content to be taught                                                    |  |  |  |  |  |  |  |  |

|----------------|-------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Lecture 1      | Zero Lecture                                                            |  |  |  |  |  |  |  |  |

| Lecture 2      | Energy signals power signals                                            |  |  |  |  |  |  |  |  |

| Lecture 3      | Continuous and discrete time signals                                    |  |  |  |  |  |  |  |  |

| Lecture 4      | Continuous amplitude signals                                            |  |  |  |  |  |  |  |  |

| Lecture 5      | and discrete amplitude signals                                          |  |  |  |  |  |  |  |  |

| Lecture 6      | System properties: linearity: additivity and homogeneity                |  |  |  |  |  |  |  |  |

| Lecture 7      | shift-invariance, causality                                             |  |  |  |  |  |  |  |  |

| Lecture 8      | stability, realizability.                                               |  |  |  |  |  |  |  |  |

| Lecture 9      | Linear shift-invariant (LSI) systems                                    |  |  |  |  |  |  |  |  |

| Lecture 10     | impulse response                                                        |  |  |  |  |  |  |  |  |

| Lecture 11     | Step response                                                           |  |  |  |  |  |  |  |  |

| Lecture 12     | Convolution.                                                            |  |  |  |  |  |  |  |  |

| Lecture 13     | Input output behavior with aperiodic convergent inputs                  |  |  |  |  |  |  |  |  |

| Lecture 14     | Characterization of causality and stability of linear shift-invariant   |  |  |  |  |  |  |  |  |

|                | systems.                                                                |  |  |  |  |  |  |  |  |

| Lecture 15     | System representation through differential equations and                |  |  |  |  |  |  |  |  |

|                | difference equations.                                                   |  |  |  |  |  |  |  |  |

| Lecture 16     | Characterization of causality and stability of linear shift-invariant   |  |  |  |  |  |  |  |  |

|                | systems.                                                                |  |  |  |  |  |  |  |  |

| Lecture 17     | System representation through differential equations and                |  |  |  |  |  |  |  |  |

|                | difference equations.                                                   |  |  |  |  |  |  |  |  |

| Lecture 18     | Periodic and semi-periodic inputs to an LSI system                      |  |  |  |  |  |  |  |  |

| Lecture 19     | The notion of a frequency response.                                     |  |  |  |  |  |  |  |  |

| Lecture 20     | Its relation to the impulse response                                    |  |  |  |  |  |  |  |  |

| Lecture 21     | Fourier series representation                                           |  |  |  |  |  |  |  |  |

| Lecture 22     | Fourier Transform                                                       |  |  |  |  |  |  |  |  |

| Lecture 23     | Convolution/multiplication and their effect in the frequency            |  |  |  |  |  |  |  |  |

|                | domain                                                                  |  |  |  |  |  |  |  |  |

| Lecture 24     | Magnitude and phase response                                            |  |  |  |  |  |  |  |  |

| Lecture 25     | Fourier domain duality.                                                 |  |  |  |  |  |  |  |  |

| Lecture 26     | The Discrete-Time Fourier Transform (DTFT) and Discrete Fourier         |  |  |  |  |  |  |  |  |

|                | Transform (DFT).                                                        |  |  |  |  |  |  |  |  |

| Lecture 27     | Parseval's Theorem. The idea of signal space and orthogonal             |  |  |  |  |  |  |  |  |

|                | bases                                                                   |  |  |  |  |  |  |  |  |

| Lecture 28     | The Laplace Transform                                                   |  |  |  |  |  |  |  |  |

| Lecture 29     | Notion of eigen functions of LSI systems Office of Dean Academic Affair |  |  |  |  |  |  |  |  |

|                | Rajasthan Technical University, 1                                       |  |  |  |  |  |  |  |  |

II Year - III Semester: B.Tech. (Electronics & Communication Engineering)

| ALL CONTRACTOR | ······································                           |

|----------------|------------------------------------------------------------------|

| Lecture 30     | A basis of eigen functions, region of convergence                |

| Lecture 31     | Poles and zeros of system, Laplace domain analysis,              |

| Lecture 32     | Solution to differential equations and system behavior.          |

| Lecture 33     | The z-Transform for discrete time signals and systems- eigen     |

|                | functions,                                                       |

| Lecture 34     | Region of convergence, z-domain analysis.                        |

| Lecture 35     | State-space analysis and multi-input, multi-output               |

|                | representation.                                                  |

| Lecture 36     | The state-transition matrix and its role.                        |

| Lecture 37     | The Sampling Theorem and its implications- Spectra of sampled    |

|                | signals.                                                         |

| Lecture 38     | Reconstruction: ideal interpolator, zero-order hold, first-order |

|                | hold, and so on                                                  |

| Lecture 39     | Aliasing and its effects.                                        |

| Lecture 40     | Relation between continuous and discrete time systems.           |

|                |                                                                  |

#### Content delivery method:

- 1. Chalk and Duster

- **2.** PPT

- **3.** Animation

- 4. Hand-outs

#### Assignments:

SYLLABUS

II Year - III Semester: B.Tech. (Electronics & Communication Engineering)

Evaluate the following sums:

(a)

$$\sum_{n=0}^{5} 2\left(\frac{3}{a}\right)^{n}$$

(b)

$$\sum_{n=2}^{6} b^{n}$$

(c)

$$\sum_{n=0}^{\infty} \left(\frac{2}{3}\right)^{2n}$$

Hint: Convert each sum to the form

$$C\sum_{n=0}^{N-1} \alpha^n = S_N$$

or  $C\sum_{n=0}^{\infty} \alpha^n = S_{\infty}$

and use the formulas

$$S_N = C\left(rac{1-lpha^N}{1-lpha}

ight), \quad S_\infty = rac{C}{1-lpha} \quad ext{ for } |lpha| < 1$$

The first-order difference equation y[n] - ay[n - 1] = x[n], 0 < a < 1, describes a particular discrete-time system initially at rest.

(a) Verify that the impulse response h[n] for this system is h[n] = a<sup>n</sup>u[n].

- (b) Is the system

- (i) memoryless?

- (ii) causal?

- (iii) stable?

Clearly state your reasoning.

(c) Is this system stable if |a| > 1?

**SYLLABUS**

**SYLLABUS**

II Year - III Semester: B.Tech. (Electronics & Communication Engineering)

#### **3EC4-06: Network Theory**

#### Max. Marks: 200 (IA:40, ETE:160)

#### 4 Credits 3L:1T:0P

#### End Term Exam: 3 Hours

| SN | Contents                                                                                                                                                                                                                                                                                                                                                                                                          | Hours |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 1  | Node and Mesh Analysis, matrix approach of network containing voltage and current sources, and reactances, source transformation and duality.                                                                                                                                                                                                                                                                     | 7     |

| 2  | Network theorems: Superposition, reciprocity, Thevenin's, Norton's,<br>Maximum power Transfer, compensation and Tallegen's theorem as<br>applied to AC. circuits.                                                                                                                                                                                                                                                 | 7     |

| 3  | Trigonometric and exponential Fourier series: Discrete spectra and<br>symmetry of waveform, steady state response of a network to non-<br>sinusoidal periodic inputs, power factor, effective values, Fourier<br>transform and continuous spectra, three phase unbalanced circuit<br>and power calculation.                                                                                                       | 8     |

| 4  | Laplace transforms and properties: Partial fractions, singularity<br>functions, waveform synthesis, analysis of RC, RL, and RLC<br>networks with and without initial conditions with Laplace<br>transforms evaluation of initial conditions                                                                                                                                                                       | 8     |

| 5  | Transient behavior, concept of complex frequency, Driving points<br>and transfer functions poles and zeros of immittance function, their<br>properties, sinusoidal response from pole-zero locations,<br>convolution theorem and Two four port network and<br>interconnections, Behaviors of series and parallel resonant circuits,<br>Introduction to band pass, low pass, high pass and band reject<br>filters. | 10    |

|    | Total                                                                                                                                                                                                                                                                                                                                                                                                             | 40    |

II Year - III Semester: B.Tech. (Electronics & Communication Engineering)

#### **Course Outcome:**

| Course<br>Code | Course<br>Name | Course<br>Outcom<br>e | Details                                                                       |  |  |  |  |  |  |

|----------------|----------------|-----------------------|-------------------------------------------------------------------------------|--|--|--|--|--|--|

|                | 5              | CO 1                  | Apply the basic circuital law and simplify the network using network theorems |  |  |  |  |  |  |

| 96             | heory          | CO 2                  | Appreciate the frequency domain techniques in different applications.         |  |  |  |  |  |  |

| 3EC4-06        | Network Theory | CO 3                  | Apply Laplace Transform for steady state and transient analysis               |  |  |  |  |  |  |

| 3]             | Netwo          | CO 4                  | Evaluate transient response and two-port network parameters                   |  |  |  |  |  |  |

|                | ſ              | CO 5                  | Analyze the series resonant and parallel resonant circuit and design filters  |  |  |  |  |  |  |

II Year - III Semester: B.Tech. (Electronics & Communication Engineering) CO-PO Mapping:

| Subject             | Course<br>Outcom<br>es | РО<br>1 | PO<br>2           | PO<br>3 | PO<br>4 | PO<br>5 | PO<br>6 | PO<br>7 | PO<br>8 | PO<br>9 | PO<br>10   | PO<br>11 | PO<br>12 |

|---------------------|------------------------|---------|-------------------|---------|---------|---------|---------|---------|---------|---------|------------|----------|----------|

| ry                  | CO 1                   | 3       | 2                 |         | 3       | 2       |         |         |         |         |            |          |          |

| l-06<br>Theory      | CO 2                   | 3       | 3                 | 1       | 2       | 2       |         |         |         |         |            |          | 1        |

| 3EC4-06<br>work The | CO 3                   | 3       | 2                 | 2       |         | 2       |         |         |         |         |            |          | 1        |

| 3EC4<br>Network     | CO 4                   | 2       | 3                 | 2       | 2       | 1       |         |         |         |         |            |          |          |

| Ne                  | CO 5                   | 2       | 3                 | 3       | 2       | 1       |         |         |         |         |            |          |          |

|                     | 2.6                    | Strong  | ~1 <del>~</del> 7 | 0       | • Mo    | dora    |         |         | 1       | ·We     | <u>_</u> 1 |          |          |

3: Strongly

2: Moderate

1: Weak

#### Lecture Plan:

| Lecture<br>No. | Content to be taught                                                             |  |  |  |  |  |

|----------------|----------------------------------------------------------------------------------|--|--|--|--|--|

| Lecture 1      | Overview of Network Theory and its significance                                  |  |  |  |  |  |

| Lecture 2      | Node and Mesh Analysis                                                           |  |  |  |  |  |

| Lecture 3      | matrix approach of network containing voltage and current sources and reactances |  |  |  |  |  |

| Lecture 4      | source transformation and duality                                                |  |  |  |  |  |

| Lecture 5      | Network theorems: Superposition and reciprocity                                  |  |  |  |  |  |

| Lecture 6      | Thevenin's and Norton's theorem                                                  |  |  |  |  |  |

| Lecture 7      | Maximum power Transfer theorem                                                   |  |  |  |  |  |

| Lecture 8      | compensation and Tallegen's theorem as applied to AC. Circuits                   |  |  |  |  |  |

| Lecture 9      | Trigonometric and exponential Fourier series                                     |  |  |  |  |  |

| Lecture 10     | Fourier series: Discrete spectra and symmetry of waveform                        |  |  |  |  |  |

| Lecture 11     | Steady state response of a network to non-sinusoidal periodic inputs             |  |  |  |  |  |

| Lecture 12     | power factor and effective values                                                |  |  |  |  |  |

| Lecture 13     | Fourier transform and continuous spectra                                         |  |  |  |  |  |

| Lecture 14     | three phase unbalanced circuit and power calculation                             |  |  |  |  |  |

| Lecture 15     | three phase unbalanced circuit and power calculation                             |  |  |  |  |  |

| Lecture 16     | Laplace transforms                                                               |  |  |  |  |  |

| Lecture 17     | Laplace transforms                                                               |  |  |  |  |  |

| Lecture 18     | Laplace transforms properties: Partial fractions                                 |  |  |  |  |  |

| Lecture 19     | singularity functions and waveform synthesis                                     |  |  |  |  |  |

| TINISION CONTRACTOR | r - III Semester: B.Tech. (Electronics & Communication Engineering) |  |  |  |  |  |  |  |  |

|---------------------|---------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Lecture 20          | nalysis of RC networks                                              |  |  |  |  |  |  |  |  |

| Lecture 21          | analysis of RL networks                                             |  |  |  |  |  |  |  |  |

| Lecture 22          | analysis of RLC networks                                            |  |  |  |  |  |  |  |  |

| Lecture 23          | Analysis of networks with and without initial conditions            |  |  |  |  |  |  |  |  |

| Lecture 24          | Analysis of networks with and without initial conditions            |  |  |  |  |  |  |  |  |

| Lecture 25          | Analysis of networks with and without initial conditions with       |  |  |  |  |  |  |  |  |

|                     | lapalace transforms evaluation                                      |  |  |  |  |  |  |  |  |

| Lecture 26          | Analysis of networks with and without initial conditions with       |  |  |  |  |  |  |  |  |

|                     | lapalace transforms evaluation of initial condition                 |  |  |  |  |  |  |  |  |

| Lecture 27          | Transient behavior                                                  |  |  |  |  |  |  |  |  |

| Lecture 28          | concept of complex frequency                                        |  |  |  |  |  |  |  |  |

| Lecture 29          | Driving points and transfer functions poles and zeros of            |  |  |  |  |  |  |  |  |

|                     | immittance function                                                 |  |  |  |  |  |  |  |  |

| Lecture 30          | Driving points and transfer functions poles and zeros of            |  |  |  |  |  |  |  |  |

|                     | immittance function: their properties                               |  |  |  |  |  |  |  |  |

| Lecture 31          | sinusoidal response from pole-zero locations                        |  |  |  |  |  |  |  |  |

| Lecture 32          | sinusoidal response from pole-zero locations                        |  |  |  |  |  |  |  |  |

| Lecture 33          | convolution theorem                                                 |  |  |  |  |  |  |  |  |

| Lecture 34          | sinusoidal response from pole-zero locations                        |  |  |  |  |  |  |  |  |

| Lecture 35          | Two four port network and interconnections                          |  |  |  |  |  |  |  |  |

| Lecture 36          | Two four port network and interconnections                          |  |  |  |  |  |  |  |  |

| Lecture 37          | Behaviors of series and parallel resonant circuits                  |  |  |  |  |  |  |  |  |

| Lecture 38          | Introduction to band pass and low pass                              |  |  |  |  |  |  |  |  |

| Lecture 39          | Introduction to high pass and reject filters                        |  |  |  |  |  |  |  |  |

| Lecture 40          | Spill over class                                                    |  |  |  |  |  |  |  |  |

| R                   | ±                                                                   |  |  |  |  |  |  |  |  |

## Content delivery method:

- **1.** Chalk and Duster

- **2.** PPT

- **3.** Hand-outs

II Year - III Semester: B.Tech. (Electronics & Communication Engineering) Sample assignments:

| Assignment 1 | Q1.         | Elaborate the significance of source                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              | Q2.         | transformation with relevant example<br>State and prove time differentiation theorem in<br>Laplace Transform                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|              | Q3.         | Find the Thevenin equivalent of the network shown in figure. What power would be delivered to a load of 100 ohms at $a$ and $b$ ?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|              |             | $20 \text{ V} \stackrel{40 \Omega}{=} \underbrace{200 \Omega}_{i_1} \stackrel{100 \Omega}{\downarrow i_1} \stackrel{0a}{\downarrow i_1} \stackrel{1}{\downarrow i_1}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Assignment 2 | Q4.         | Calculate Thevenin equivalent circuit with respect to terminals <i>a</i> and <i>b</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|              |             | $-j300 \Omega$ $($ 200 $\Omega$ $j100 \Omega$ $($ $100 / 0^{\circ} V $ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $)$ $($ $($ $)$ $($ $($ $)$ $($ $($ $)$ $($ $($ $)$ $($ $($ $)$ $($ $($ |

|              | <b>Q</b> 5. | Derive transient current and voltage responses of sinusoidal driven RL and RC circuits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|              | Q6.         | Specify the restrictions on pole and zero locations for transfer functions and driving-point functions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

**SYLLABUS**

II Year - III Semester: B.Tech. (Electronics & Communication Engineering)

#### **3EC4-07: Electronic Devices**

#### 4 Credits 3L:1T:0P

#### Max. Marks: 200 (IA:40, ETE:160) End Term Exam: 3 Hours

| SN | Contents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Hours |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 1  | Introduction to Semiconductor Physics: Introduction, Energy<br>band gap structures of semiconductors, Classifications of<br>semiconductors, Degenerate and non-degenerate semiconductors,<br>Direct and indirect band gap semiconductors, Electronic<br>properties of Silicon, Germanium, Compound Semiconductor,<br>Gallium Arsenide, Gallium phosphide & Silicon carbide, Variation<br>of semiconductor conductivity, resistance and bandgap with<br>temperature and doping. Thermistors, Sensitors. | 6     |

| 2  | Review of Quantum Mechanics, Electrons in periodic Lattices, E-k diagrams. Energy bands in intrinsic and extrinsic silicon; Carrier transport: diffusion current, drift current, mobility and resistivity; sheet resistance, design of resistors.                                                                                                                                                                                                                                                      | 6     |

| 3  | Generation and recombination of carriers; Poisson and continuity<br>equation P-N junction characteristics, I-V characteristics, and<br>small signal switching models; Avalanche breakdown,<br>Zener diode, Schottky diode.                                                                                                                                                                                                                                                                             | 8     |

| 4  | Bipolar Junction Transistor, I-V characteristics, Ebers-Moll<br>Model, MOS capacitor, C-V characteristics, MOSFET, I-V<br>characteristics, and small signal models of MOS transistor, LED,<br>photodiode and solar cell.                                                                                                                                                                                                                                                                               | 11    |

| 5  | Integrated circuit fabrication process: oxidation, diffusion, ion<br>implantation, Photolithography, etching, chemical vapor<br>deposition, sputtering, twin-tub CMOS process.                                                                                                                                                                                                                                                                                                                         | 9     |

|    | Total                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 40    |

II Year - III Semester: B.Tech. (Electronics & Communication Engineering)

#### **Course Outcome:**

| Course<br>Code | Course<br>Name | Course<br>Outco<br>me | Details                                                                                                                 |