## **Techno India NJR Institute of Technology**

Department of Electronics & Communication Engineering

B.Tech. III Semester

Lab: Digital System Design (3EC4-22)

### RAJASTHAN TECHNICAL UNIVERSITY, KOTA

### **SYLLABUS**

II Year - III Semester: B.Tech. (Electronics & Communication Engineering)

3EC4-22: Digital System Design Lab

1 Credit Max. Marks: 50 (IA:30, ETE:20)

OL:OT:2P

List of Experiments

| Dist Gi | Experiments                                                                                                                                                                                        |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| S.No.   | Name of Experiment                                                                                                                                                                                 |

| Part A: | Combinational Circuits                                                                                                                                                                             |

| 1.      | To verify the truth tables of logic gates: AND, OR, NOR, NAND, NOR, Ex-OR and Ex-NOR                                                                                                               |

| 2.      | To verify the truth table of OR, AND, NOR, Ex-OR, Ex-NOR logic gates realized using NAND & NOR gates.                                                                                              |

| 3.      | To realize an SOP and POS expression.                                                                                                                                                              |

| 4.      | To realize Half adder/ Subtractor& Full Adder/ Subtractor using NAND & NOR gates and to verify their truth tables                                                                                  |

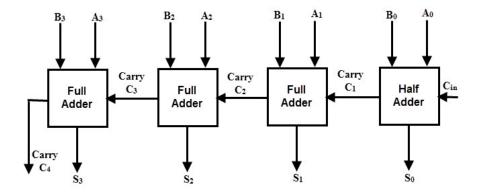

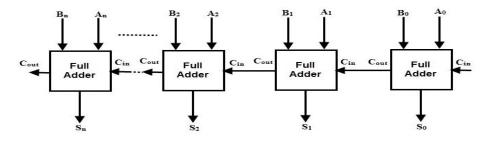

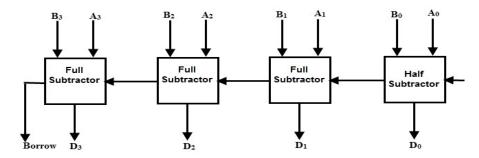

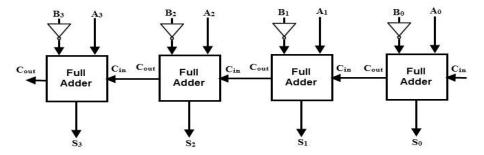

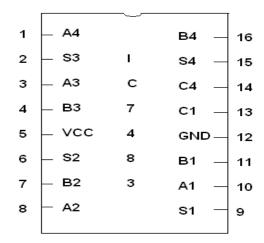

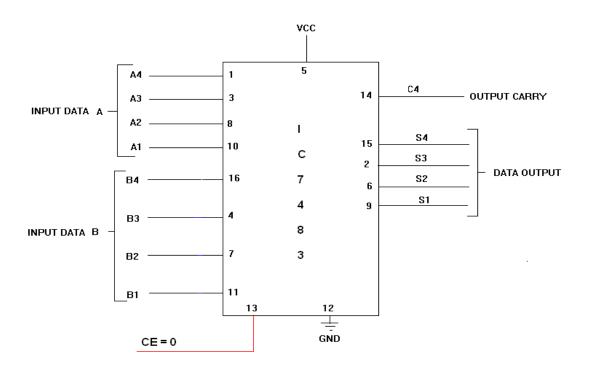

| 5.      | To realize a 4-bit ripple adder/ Subtractor using basic Half adder/ Subtractor& basic Full Adder/ Subtractor.                                                                                      |

| 6.      | To design 4-to-1 multiplexer using basic gates and verify the truth table. Also verify the truth table of 8-to-1 multiplexer using IC                                                              |

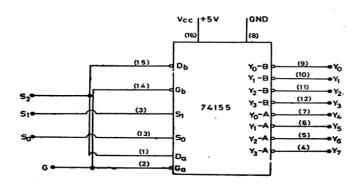

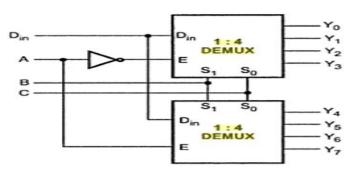

| 7.      | To design 1-to-4 demultiplexer using basic gates and verify the truth table. Also to construct 1-to-8 demultiplexer using blocks of 1-to-4 demultiplexer                                           |

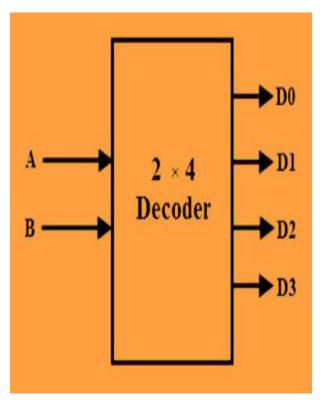

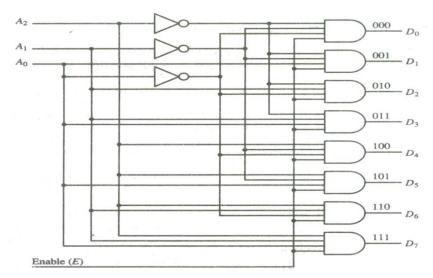

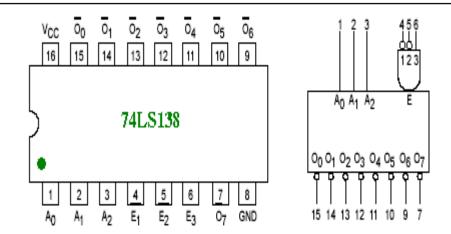

| 8.      | To design 2x4 decoder using basic gates and verify the truth table. Also verify the truth table of 3x8 decoder using IC                                                                            |

| 9.      | Design & Realize a combinational circuit that will accept a 2421 BCD code and drive a TIL -312 seven-segment display                                                                               |

| Part B: | Sequential Circuits                                                                                                                                                                                |

| 10.     | Using basic logic gates, realize the R-S, J-K and D-flip flops with and without clock signal and verify their truth table.                                                                         |

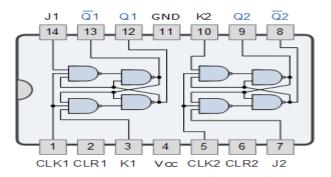

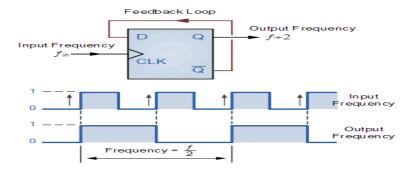

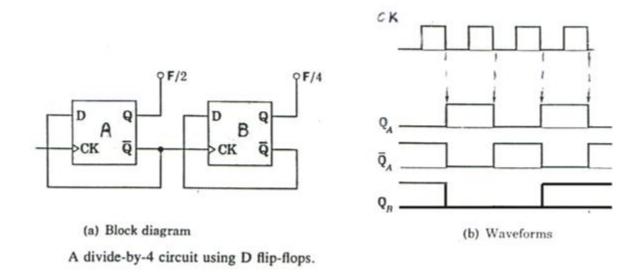

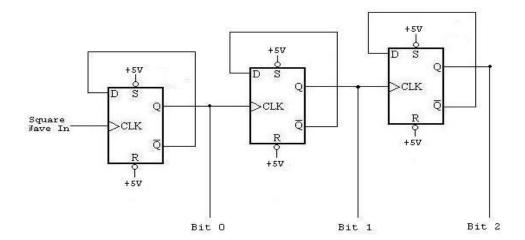

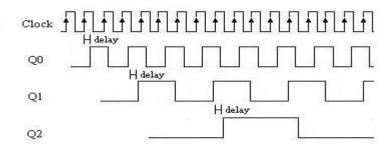

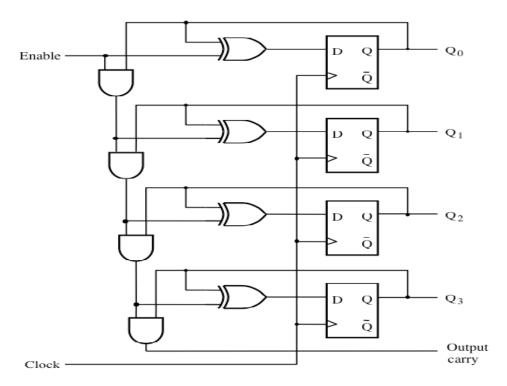

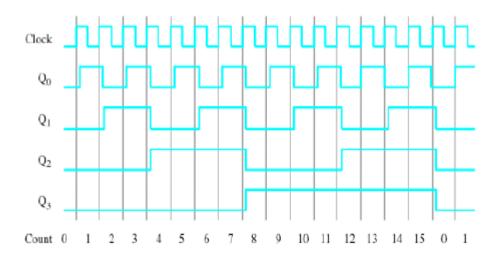

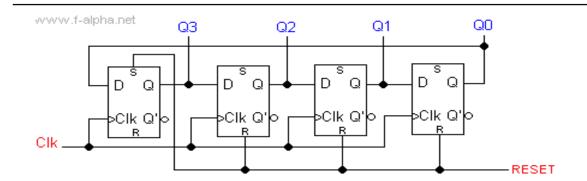

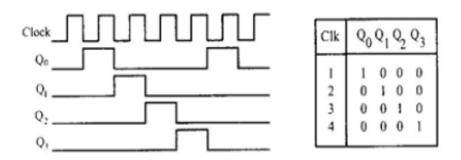

| 11.     | Construct a divide by 2, 4 & 8 asynchronous counter. Construct a 4-bit binary counter and ring counter for a particular output pattern using D flip flop.                                          |

| 12.     | Design and construct unidirectional shift register and verify the                                                                                                                                  |

| 13.     | Design and construct BCD ripple counter and verify the function.                                                                                                                                   |

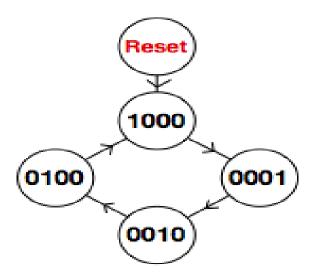

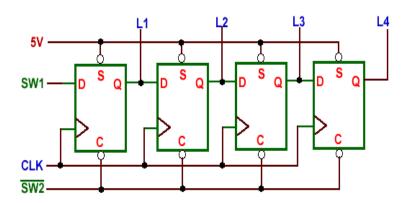

| 14.     | Design and construct a 4 Bit Ring counter and verify the function                                                                                                                                  |

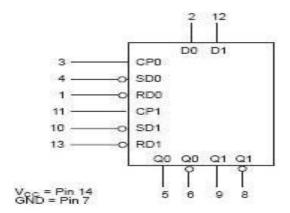

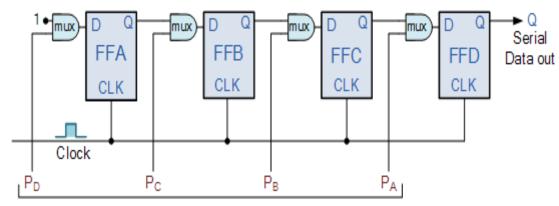

| 15.     | Perform input/output operations on parallel in/Parallel out and Serial in/Serial out registers using clock. Also exercise loading only one of multiple values into the register using multiplexer. |

Note: Minimum 6 experiments to be conducted from Part-A& 4 experiments to be conducted from Part-B.

Office of Dean Academic Affairs

Rajasthan Technical University, Kota

## RAJASTHAN TECHNICAL UNIVERSITY, KOTA

### **SYLLABUS**

II Year - III Semester: B.Tech. (Electronics & Communication Engineering)

#### **Course Outcome:**

| Course<br>Code | Cours<br>e<br>Name           | Course<br>Outcome | Details                                                                      |

|----------------|------------------------------|-------------------|------------------------------------------------------------------------------|

|                |                              | CO 1              | To verify TTL IC's functionality with the data sheets.                       |

| 22             | stem<br>,ab                  | CO 2              | To minimize the complexity of digital logic circuits.                        |

| 3EC4-2         | Digital Syste:<br>Design Lab | CO 3              | To design and analyse combinational logic circuits.                          |

| 3E             | gita<br>Jes                  | CO 4              | To design and analyse sequential logic circuits.                             |

|                | Dig<br>I                     | CO 5              | Able to implement applications of combinational & sequential logic circuits. |

### **CO-PO Mapping:**

| Subject                          | Course<br>Outcom<br>es | PO<br>1 | PO 2 | PO<br>3 | PO<br>4 | PO 5 | PO 6 | PO 7 | PO<br>8 | PO<br>9 | PO<br>10 | PO<br>11 | PO<br>12 |

|----------------------------------|------------------------|---------|------|---------|---------|------|------|------|---------|---------|----------|----------|----------|

| n                                | CO 1                   | 3       | 3    | 1       |         |      |      |      |         |         |          |          | 1        |

| 4-22<br>System<br>n Lab          | CO 2                   | 3       | 3    | 2       | 1       | 1    |      |      |         |         |          |          | 1        |

| 3EC4-22<br>ital Syst<br>esign La | CO 3                   | 3       | 3    | 3       | 2       | 3    | 1    |      |         |         |          |          | 2        |

| 3EC4.<br>Digital Sy<br>Design    | CO 4                   | 3       | 3    | 3       | 2       | 3    | 1    |      |         |         |          |          | 2        |

| D                                | CO 5                   | 3       | 3    | 3       | 3       | 3    | 3    |      |         |         |          |          | 3        |

3: Strongly 2: Moderate 1: Weak

Office of Dean Academic Affairs Rajasthan Technical University, Kota

### **Instructions for the Lab**

### **DO'S**

- 1. Student should get the record of previous experiment checked before starting the new experiment.

- 2. Read the manual carefully before starting the experiment.

- 3. Before starting the experiment, get circuit diagram checked by the teacher.

- 4. Before switching on the power supply, get the circuit connections checked.

- 5. Get your readings checked by the teacher.

- 6. Apparatus must be handled carefully.

- 7. Maintain strict discipline.

- 8. Keep your mobile phone switched off or in vibration mode.

- 9. Students should get the experiment allotted for next turn, before leaving the lab.

### **DON'TS**

- 1. Do not touch or attempt to touch the mains power supply wire with bare hands.

- 2. Do not overcrowd the tables.

- 3. Do not tamper with equipment's.

- 4. Do not leave the lab without permission from the teacher.

#### <u>Introduction to the DSD – Lab</u>

Digital System Design is the Lab of electronics and computer science that deals with the digital inputs and outputs to perform various tasks. It is based upon the digital design methodologies and consists of digital circuits, IC's and logic gates. It uses only binary digits, i. e. either '0' or '1'.

We know there are two types of signals, one is analog or continuous signal and the second one is Digital or discrete signal. Now coming to the area of Digital system design, it is essential to understand wide range of applications from industrial electronics to the fields of communication, from micro embedded systems to military equipment. The main and perhaps the most revolutionary advantage of digital system design is the decrease in size and the improvement in technology.

The world of electronics was initially dominated by analogue signals—that is, signals representing a continuous range of values. In digital circuitry, however, there are only two states: on and off, also referred to as 1 and 0, respectively. Digital information has its roots back in the Victorian era thanks to George Boole, who developed the idea of Boolean algebra. Every aspect of our lives is increasingly becoming integrated and connected by the Internet of Things (IoT), which consists of computers and embedded systems. These devices are controlled by software which at its core is Boolean logic in conjunction with digital information. The world around us is analogue, but with every passing day our interaction with the world is becoming more digital and more integrated.

Some general things to know in this lab are:

#### • Bread Board/ Proto Board

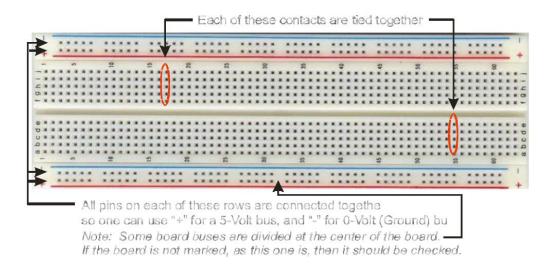

Figure 1: Bread Board and internal connections

Your kit includes a plastic board used to wire together electric circuits. This is called a breadboard or a proto board, since it is used to prototype circuits. Figure 1 above shows how the terminals are connected internally inside the board. The horizontal connections X and Y are called buses and are usually for power and ground.

Usually, the top row is connected to the +5V power supply and is called the power bus. The bottom row is connected to an external ground and is called the ground bus.

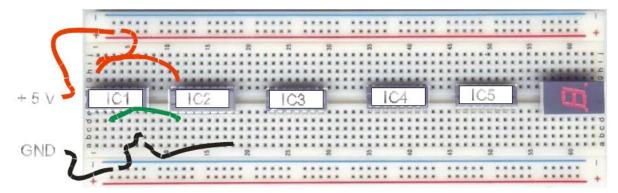

Figure 2 shows how the power and ground pins of IC1 and IC2 can be connected together by the red wires and black wires. It also shows how the output of pin 3 on IC1 can be connected to the input pin 1 of IC2 with a green wire.

Figure 2: Connecting Wires

Special care is needed when using the protoboard. If a wire which is too large is forced into one of the holes, that particular contact point most probably will be damaged. As a result, the next time the protoboard is used and a wire is inserted into that hole, the wire may not make contact with the internal connection strip and the circuit will not operate properly.

An even more aggravating situation is when the wire makes contact only part of the time. This is called an "intermittent fault." Since the circuit will operate correctly part of the time, and then mysteriously fail, this type of fault is very hard to find. A good rule to follow is: if the wire doesn't go in easily, find another wire. Pay particular attention to components such as resistors, capacitors - etc., since many have lead with diameters which allow insertion into the protoboard, but still cause damage to the contacts.

To avoid damage, do not insert wires too far.

You will have to strip the wire leads before using them to interconnect circuits on your protoboards. The proper way to do this is to use a pair of wire cutters to carefully strip ¼ inch of insulation off of each end of the wire, taking care not to nick the copper wire. If you take more than a quarter inch off, you risk having wire exposed above the protoboard, which will cause a short if it touches another lead or IC pin. If you cut less that a quarter off, the wire may not make a good connection within the protoboard hole. It also helps to cut the ends of

the wire at an angle, which produces a point on the end of the wire. The wire will then slide into the protoboard easier.

### • Integrated Circuits (IC's)

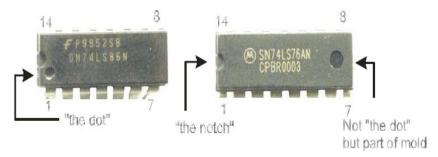

The IC's are main components for DSD lab. Each looks similar to the one shown below:

Figure 3: Physical view of IC

Note the numbering system, which progresses counter-clockwise from pin 1. Pin 1 is designated by a dot or a notch Usually on TTL logic, the last pin is to be connected to the +5 V supply, and the pin diagonally opposite is connected to ground. These are pins 14 and 7, respectively, for 14-pin IC's and 16 and 8 for 16-pin IC's.

There are some exceptions to this rule, so always check!

Special caution should be taken when inserting and removing IC's from the protoboard.

When shipped from the factory, the leads (legs) of the IC's are slightly bent apart to aid in machine insertion. It is necessary to straighten the legs prior to insertion into the protoboards.

From factory. Bend one side, then the other, till legs are parallel.

Figure 4: Bending in ICs

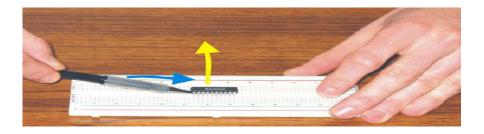

When you remove a chip (IC) from the protoboard, it is very easy to bend the legs by not exercising caution. You should not simply pull on the chip with two fingers to remove it. One end will invariably rise before the other causing the legs on the other end to bend. It may even result in a puncture wound to one of your fingers because the legs of the IC's are very

sharp. Be careful! If an IC extractor is not available, you should use the tip of a pen or pencil to gently pry up the legs on one end of the chip, and then the other, as shown below. Usually, if a leg is bent twice, it will break off easily and the IC is virtually useless so.

#### **GOOD LAB PROCEDURES**

In order to make your experiments go easier, there are some procedures which should be followed. Most are generally common sense.

Figure 5: Correct way of removing any IC from breadboard

• Before wiring a circuit, a circuit diagram should be drawn and simulated. This diagram should include pin numbers as shown below.

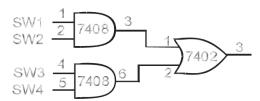

Figure 6: Circuit connection diagram including IC pin numbers

You can then check off each connection as it is wired. For example, after the top AND gate is connected to the OR gate on the right, the line connecting them in the diagram should be checked off as having been wired. Without some system like this, it is very easy to forget which gate is which within a system.

- While wiring, rewiring, etc. *turn off the power*. This prevents the application of power to the circuit in unwanted places.

- Try to avoid messy "rat's nest" wiring. It is almost impossible to trouble-shoot a messy wiring job. It is also hard to make changes to a disorganized board. Keep lead wires as short as possible, and make neat, flat bends. It is also smart not to wire across the top of the IC's.

Wire the power leads of chips first, using a color scheme if possible. Traditionally,  $\mathbf{RED} = +5$  Volts and  $\mathbf{BLACK} = \mathbf{Ground}$

### Experiment No. – 1

<u>Aim:</u> To verify the truth tables of logic gates: AND, OR, NOT, NAND, NOR, Ex-OR and Ex-NOR

Apparatus / Component Required: IC tester, Digital trainer kit and Digital ICs

| COMPONENT     | SPECIFICATION                                                                                                                                                                                                                                                                                                  |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| COM ONEM      | STEER TOTAL                                                                                                                                                                                                                                                                                                    |

| 2 i/p AND     | IC 7408                                                                                                                                                                                                                                                                                                        |

| GATE          |                                                                                                                                                                                                                                                                                                                |

| 2 i/p OR GATE | IC 7432                                                                                                                                                                                                                                                                                                        |

| NOT GATE      | IC 7404                                                                                                                                                                                                                                                                                                        |

| 2 i/p XOR     | IC 7486                                                                                                                                                                                                                                                                                                        |

| GATE          |                                                                                                                                                                                                                                                                                                                |

| 2 i/p NAND    | IC 7400                                                                                                                                                                                                                                                                                                        |

| GATE          | IC 7402                                                                                                                                                                                                                                                                                                        |

| 2 i/p NOR     |                                                                                                                                                                                                                                                                                                                |

| GATE          | IC 7410                                                                                                                                                                                                                                                                                                        |

|               | IC 7411                                                                                                                                                                                                                                                                                                        |

| 3 i/p NAND    | IC 7427                                                                                                                                                                                                                                                                                                        |

| GATE          |                                                                                                                                                                                                                                                                                                                |

| 3 i/p AND     |                                                                                                                                                                                                                                                                                                                |

| GATE          |                                                                                                                                                                                                                                                                                                                |

| 3 i/p NOR     |                                                                                                                                                                                                                                                                                                                |

| GATE          |                                                                                                                                                                                                                                                                                                                |

| 4 i/p NAND    | IC 7420                                                                                                                                                                                                                                                                                                        |

| GATE          | IC 7421                                                                                                                                                                                                                                                                                                        |

| 4 i/p AND     | IC 7425                                                                                                                                                                                                                                                                                                        |

| GATE          |                                                                                                                                                                                                                                                                                                                |

| 4 i/p NOR     |                                                                                                                                                                                                                                                                                                                |

| GATE          |                                                                                                                                                                                                                                                                                                                |

|               |                                                                                                                                                                                                                                                                                                                |

|               |                                                                                                                                                                                                                                                                                                                |

| 2 i/p Ex-NOR  | IC74266                                                                                                                                                                                                                                                                                                        |

| GATE          |                                                                                                                                                                                                                                                                                                                |

|               |                                                                                                                                                                                                                                                                                                                |

|               |                                                                                                                                                                                                                                                                                                                |

|               | GATE 2 i/p OR GATE NOT GATE 2 i/p XOR GATE 2 i/p NAND GATE 2 i/p NOR GATE 3 i/p NAND GATE 3 i/p AND GATE 3 i/p AND GATE 4 i/p NAND GATE 4 i/p NAND GATE 4 i/p NAND GATE 4 i/p AND GATE 5 i/p NOR GATE 6 i/p AND GATE 7 i/p NOR GATE 7 i/p NOR GATE |

#### **Theory:**

#### **BASIC GATES:**

### The Digital Logic "AND" Gate

A Logic AND Gate is a type of digital logic gate that has an output which is normally at logic level "0" and only goes "HIGH" to a logic level "1" when ALL of its inputs are at logic level "1". The output of a Logic AND Gate only returns "LOW" again when ANY of its inputs are at a logic level "0". The logic or Boolean expression given for a logic AND gate is that for *Logical Multiplication* which is denoted by a single dot or full stop symbol, (.) giving us the Boolean expression of: A.B = Q.

Then we can define the operation of a 2-input logic AND gate as being:

### "If both A and B are true, then Q is true"

### 2-input AND Gate

| Symbol                                         | Truth Table             |   |   |  |

|------------------------------------------------|-------------------------|---|---|--|

|                                                | В                       | A | Q |  |

| A O & Q B O 2-input AND Gate                   | 0                       | 0 | 0 |  |

|                                                | 0                       | 1 | 0 |  |

|                                                | 1                       | 0 | 0 |  |

|                                                | 1                       | 1 | 1 |  |

| Boolean Expression $\mathbf{Q} = \mathbf{A.B}$ | Read as A AND B gives Q |   |   |  |

Figure 1.1: Logic symbol and truth table of AND gate

Commonly available digital logic AND gate IC's included:

### TTL Logic Types

### • 74LS08 Quad 2-input

### • 74LS11 Triple 3-input

• 74LS21 Dual 4-input

#### **CMOS Logic Types**

- CD4081 Quad 2-input

- CD4073 Triple 3-input

- CD4082 Dual 4-input

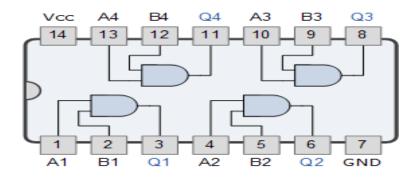

### **Quad 2-Input AND Gate IC 7408**

Figure 1.2: Pin diagram of IC 7408

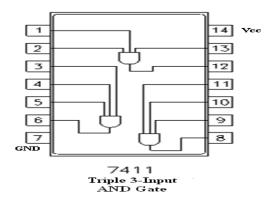

### **Triple 3-input AND Gate IC 7411**

Figure 1.3: Pin diagram of IC 7411

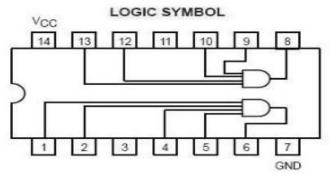

### **Dual 4-input AND Gate IC 7421**

74ALS21 Dual 4-Input AND Gate

Figure 1.4: Pin diagram of IC 7421

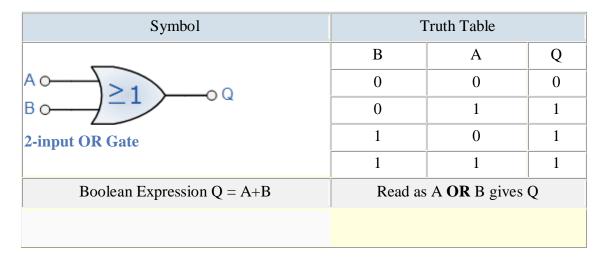

### The Logic "OR" Gate

A Logic OR Gate or Inclusive-OR gate is a type of digital logic gate that has an output which is normally at logic level "0" and only goes "HIGH" to a logic level "1" when ANY of its inputs are at logic level "1". The output of a Logic OR Gate only returns "LOW" again when ALL of its inputs are at a logic level "0". The logic or Boolean expression given for a logic OR gate is that for *Logical Addition* which is denoted by a plus sign, (+) giving us the Boolean expression of: A+B=Q.

Then we can define the operation of a 2-input logic OR gate as being:

### "If either A or B is true, then Q is true"

### 2-input OR Gate

Figure 1.5: Logic symbol and truth table of OR Gate

Commonly available OR gate IC's included:

### TTL Logic Types CMOS Logic Types

- 74LS32 Quad 2-input

- CD4071 Quad 2-input

- CD4075 Triple 3-input

- CD4072 Dual 4-input

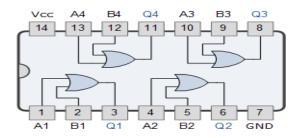

### **Quad 2-Input OR Gate IC 7432**

Figure 1.6: Pin diagram of IC 7432

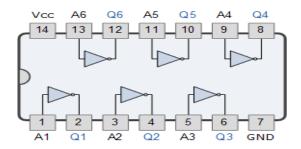

### The Digital Logic "NOT" Gate (Digital Inverter)

The digital Logic NOT Gate is the most basic of all the logical gates and is sometimes referred to as an Inverting Buffer or simply a Digital Inverter. It is a single input device which has an output level that is normally at logic level "1" and goes "LOW" to a logic level "0" when its single input is at logic level "1", in other words it "inverts" (complements) its input signal. The output from a **NOT** gate only returns "HIGH" again when its input is at logic level "0" giving us the Boolean expression of: A = Q.

Then we can define the operation of a single input logic NOT gate as being:

### "If A is NOT true, then Q is true"

| Symbol                              | Truth Table    |                |  |

|-------------------------------------|----------------|----------------|--|

|                                     | A              | Q              |  |

| $AO \longrightarrow 1$              | 0              | 1              |  |

| Inverter or NOT Gate                | 1              | 0              |  |

| Boolean Expression $Q = not A or A$ | Read as invers | e of A gives Q |  |

Figure 1.7: Logic symbol and truth table of OR gate

Then, with an input voltage at "A" HIGH, the output at "Q" will be LOW and an input voltage at "A" LOW the Resulting output voltage at "Q" is HIGH producing the complement of the input signal. Commonly available logic NOT gate and Inverter IC's include

### TTL Logic Types

- 74LS04 Hex Inverting NOT Gate

- 74LS04 Hex Inverting NOT Gate

- 74LS14 Hex Schmitt Inverting NOT Gate

- 74LS1004 Hex Inverting Drivers

### **CMOS Logic Types**

- CD4009 Hex Inverting NOT Gate

- CD4069 Hex Inverting NOT Gate

#### **Hex Inverter Gate IC 7404**

Figure 1.8: Pin diagram of IC 7404

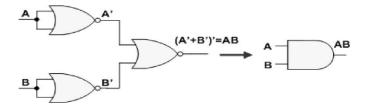

### **UNIVERSAL GATES:**

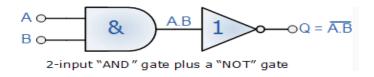

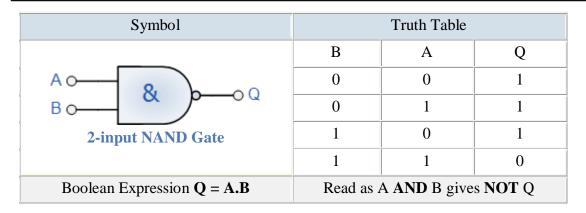

### The Logic "NAND" Gate

The Logic NAND Gate is a combination of the digital logic AND gate with that of an inverter or NOT gate connected together in series. The NAND (Not - AND) gate has an output that is normally at logic level "1" and only goes "LOW" to logic level "0" when ALL of its inputs are at logic level "1". The Logic NAND Gate is the reverse or "Complementary" form of the AND gate we have seen previously.

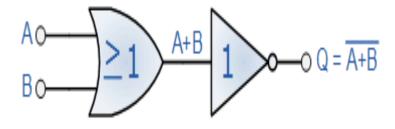

### **Logic NAND Gate Equivalence**

Figure 1.9: Equivalent circuit of NAND gate using AND and NOT gate

The logic or Boolean expression given for a logic NAND gate is that for Logical Addition, which is the opposite to the AND gate, and which it performs on the complements of the inputs. The Boolean expression for a logic NAND gate is denoted by a single dot or full stop symbol, (.) with a line or Overline, ( —) over the expression to signify the NOT or logical negation of the NAND gate giving us the Boolean expression of: A.B = Q. Then we can define the operation of a 2-input logic NAND gate as being:

"If either A or B are NOT true, then Q is true"

Figure 1.10: Logic symbol and truth table of NAND gate

Commonly available logic NAND gate IC's including:

### **TTL Logic Types**

- 74LS00 Quad 2-input

- 74LS10 Triple 3-input

- 74LS20 Dual 4-input

- 74LS30 Single 8-input

### **CMOS Logic Types**

- CD4011 Quad 2-input

- CD4023 Triple 3-input

- CD4012 Dual 4-input

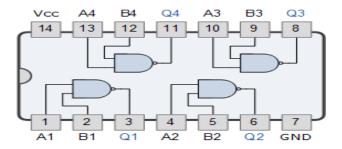

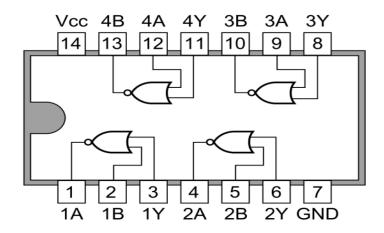

### **Quad 2-Input NAND Gate IC 7400**

Figure 1.11: Pin diagram of IC 7400

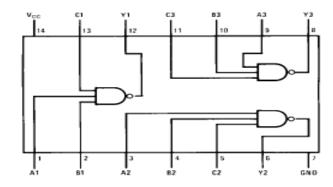

### **Triple 3-Input NAND Gate IC 7410**

Figure 1.12: Pin diagram of IC 7410

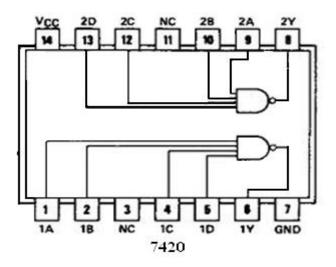

### **Dual 4-Input NAND Gate IC 7420**

Figure 1.13: Pin diagram of IC 7420

### The Logic "NOR" Gate

The Logic NOR Gate or Inclusive-NOR gate is a combination of the digital logic OR gate with that of an inverter or NOT gate connected together in series. The NOR (Not - OR) gate has an output that is normally at logic level "1" and only goes "LOW" to logic level "0" when ANY of its inputs are at logic level "1". The Logic NOR Gate is the reverse or "Complementary" form of the OR gate we have seen previously.

### **NOR Gate Equivalent**

2-input "OR" gate plus a "NOT" gate

Figure 1.14: Equivalent circuit of NOR gate using OR and NOT gate

The logic or Boolean expression given for a logic NOR gate is that for Logical Multiplication which it performs on the complements of the inputs. The Boolean expression for a logic NOR gate is denoted by a plus sign, (+) with a line or Over line, (-) over the expression to signify the NOT or logical negation of the NOR gate giving us the Boolean expression of: A+B=Q. Then we can define the operation of a 2-input logic NOR gate as being:

"If both A and B are NOT true, then Q is true"

| Symbol                                                    | Truth Table                |   |   |

|-----------------------------------------------------------|----------------------------|---|---|

| A ○                                                       | В                          | A | Q |

|                                                           | 0                          | 0 | 1 |

|                                                           | 0                          | 1 | 0 |

| 2-input NOR Gate                                          | 1                          | 0 | 0 |

|                                                           | 1                          | 1 | 0 |

| Boolean Expression $\mathbf{Q} = \mathbf{A} + \mathbf{B}$ | Read as A OR B gives NOT Q |   |   |

Figure 1.15: Logic symbol and truth table of NOR gate

Commonly available NOR gate IC's include:

### TTL Logic Types

### • 74LS02 Quad 2-input

- 74LS27 Triple 3-input

- 74LS260 Dual 4-input

#### **CMOS Logic Types**

- CD4001 Quad 2-input

- CD4025 Triple 3-input

- CD4002 Dual 4-input

### **Quad 2-Input NOR Gate 7402**

Figure 1.16: Pin diagram of IC 7402

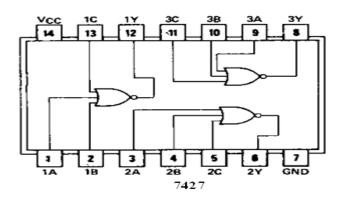

### **Triple 3-Input NOR Gate IC 7427**

Figure 1.17: Pin diagram of IC 7427

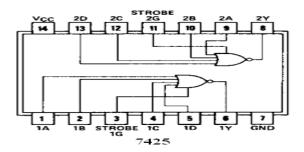

### **Dual 4-Input NOR Gate IC 7425**

Figure 1.18: Pin diagram of IC 7425

### The Exclusive-OR Gate (Ex-OR Gate)

The output of an Exclusive-OR gate ONLY goes "HIGH" when its two input terminals are at "DIFFERENT" logic levels with respect to each other and they can both be at logic level "1" or both at logic level "0" giving us the Boolean expression of: Q = A'B + AB'. The Exclusive-OR Gate function is achieved is achieved by combining standard gates together to form more complex gate functions. An example of a 2-input Exclusive-OR gate is given below.

### 2-input Ex-OR Gate

| Symbol                                 | Truth Table                      |     |   |  |

|----------------------------------------|----------------------------------|-----|---|--|

|                                        | В                                | A   | Q |  |

| $A \circ A \circ A \circ Q$            | 0                                | 0   | 0 |  |

|                                        | 0                                | 1   | 1 |  |

| 2-input Ex-OR Gate                     | 1                                | 0   | 1 |  |

|                                        | 1                                | 1   | 0 |  |

| Boolean Expression $Q = A \bigoplus B$ | Read as A OR B but NOT BOTH give | s Q |   |  |

| TTL Logic Types                        | CMOS Logic Types                 |     |   |  |

| • 74LS86 Quad 2-input                  | • CD4030 Quad 2-input            |     |   |  |

Figure 1.19: Logic symbol and truth table of XOR gate

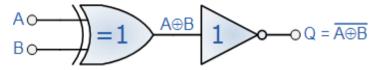

### Quad 2-Input Ex-OR Gate IC 7486

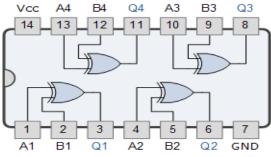

Figure 1.20: Pin diagram of IC 7486

### **The Exclusive-NOR Gate**

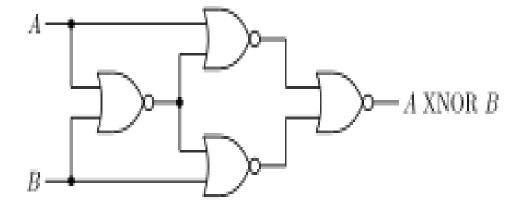

The output of an Exclusive-NOR gate ONLY goes "HIGH" when its two input terminals, A and B are at the "SAME" logic level which can be either at a logic level "1" or at a logic level "0". Then this type of gate gives and output "1" when its inputs are "logically equal" or "equivalent" to each other, which is why an Exclusive-NOR gate is sometimes called an Equivalence Gate.

### **Ex-NOR Gate Equivalent**

2-input "Ex-OR" gate plus a "NOT" gate

Figure 1.21: Equivalent circuit of XNOR gate using XOR – NOT gate

| Symbol                                                            | Truth Table                      |   |   |  |

|-------------------------------------------------------------------|----------------------------------|---|---|--|

|                                                                   | В                                | A | Q |  |

| $\begin{array}{c} A \circ \\ B \circ \end{array} = 1  \bigcirc Q$ | 0                                | 0 | 1 |  |

|                                                                   | 0                                | 1 | 0 |  |

| 2-input Ex-NOR Gate                                               | 1                                | 0 | 0 |  |

|                                                                   | 1                                | 1 | 1 |  |

| Boolean Expression Q = A XNOR B                                   | Read if A AND B the SAME gives Q |   |   |  |

Figure 1.22: Logic symbol and truth table of XNOR gate

In general, an Exclusive-NOR gate will give an output value of logic "1" ONLY when there are an EVEN number of 1's on the inputs to the gate (the inverse of the Ex-OR gate) except when all its inputs are "LOW". Commonly available Exclusive-NOR gate IC's include:

TTL Logic Types

74LS266 Quad 2-input

CD4077 Quae

CD4077 Quad 2-input

### **Quad 2-Input Ex-NOR Gate IC 74267**

Figure 1.23: Pin diagram of IC 74267

### **Procedure:**

- Test the digital ICs with the help of IC tester.

- Make the connections on the breadboard as per the pin diagram. Connect the inputs of any logic gate to the logic sources and its output to the logic indicator.

- Apply various input combinations and observe output for each one.

- Verify the truth table for each input/ output combination.

- Repeat the process for all other logic gates.

<u>Output</u>: The truth tables of logic gates: AND, OR, NOT, NAND, NOR Ex-OR and Ex-NOR are verified using their ICs.

**Result:** In conclusion, each basic gate works in unique way, which is proved during this experiment. We used the truth table to examine the operation of the basic logic gate. It is proved from experiment that logic gates work in basis of Boolean Algebra. AND Gate, OR Gate and NOT Gate are the basic gates. All the combinational logic gates are made of these three basic gates. Output from one logic gate can be used as input for another logic gate to form combinational logic gate. So, we have studied how logic gates work on the basis of Boolean algebra.

#### **Discussions:**

- Q1. Define the term digital and analog.

- Q2. What is IC?

- Q3. Define the Basic and universal gates.

- Q4. If a 3-input NOR gate has eight input possibilities, how many of those possibilities will Result in a HIGH output?

- Q5. Which of the logical operations is represented by the + sign in Boolean algebra?

- Q5. How many no. of input variables can a NOT Gate have?

### Experiment No - 2

<u>Aim:</u> To verify the truth table of OR, AND, NOR, NAND, NOT, Ex-OR and Ex-NOR logic gates realized using NAND & NOR gates.

Apparatus / Component Required: IC tester, Digital trainer kit, Digital ICs (7400, 7402)

### **Theory**:

#### <u>Universal Gates (NAND & NOR Gates):</u>

A universal gate is a gate which can implement any Boolean function without need to use any other gate type. The NAND and NOR gates are universal gates. This is advantageous since NAND and NOR gates are economical and easier to fabricate.

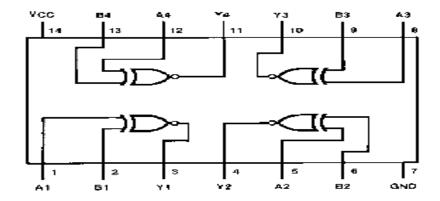

### **NAND Gate is a Universal Gate:**

To prove that any Boolean function can be implemented using only NAND gates, we will show that the AND, OR, and NOT operations can be performed using only these gates.

### Implementing an Inverter Using only NAND Gate

The figure shows two ways in which a NAND gate can be used as an inverter (NOT gate).

1. All NAND input pins connect to the input signal A gives an output A'.

Figure 2.1

2. One NAND input pin is connected to the input signal A while all other input pins are connected to logic 1. The output will be A'.

Figure 2.2

### Implementing AND Using only NAND Gates

3. An AND gate can be replaced by NAND gates as shown in the figure (The AND is replaced by a NAND gate with its output complemented by a NAND gate inverter).

Figure 2.3

### **Implementing OR Using only NAND Gates**

4. An OR gate can be replaced by NAND gates as shown in the figure (The OR gate is replaced by a NAND gate with all its inputs complemented by NAND gate inverters).

Figure 2.4

Thus, the NAND gate is a universal gate since it can implement the AND, OR and NOT functions.

### **Implementing NOR Using only NAND Gates**

Figure 2.5

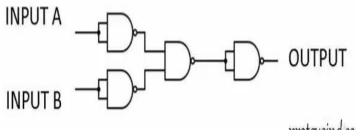

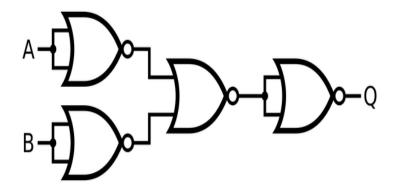

### **Implementing EX-OR Using only NAND Gates**

Figure 2.6

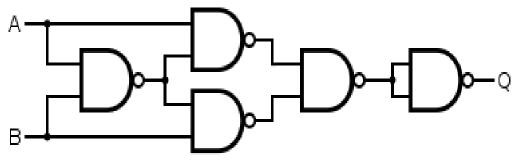

### **Implementing EXNOR Using only NAND Gates**

Figure 2.7

### **NOR Gate is a Universal Gate:**

To prove that any Boolean function can be implemented using only NOR gates, we will show that the AND, OR, and NOT operations can be performed using only these gates.

### Implementing an Inverter Using only NOR Gate

The figure shows two ways in which a NOR gate can be used as an inverter (NOT gate).

1. All NOR input pins connect to the input signal A gives an output A'.

Figure 2.8

**2.** One NOR input pin is connected to the input signal A while all other input pins are connected to logic 0. The output will be A.

Figure 2.9

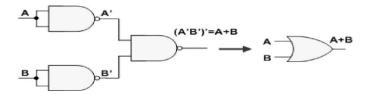

### Implementing OR Using only NOR Gates

An OR gate can be replaced by NOR gates as shown in the figure (The OR is replaced by a NOR gate with its output complemented by a NOR gate inverter)

Figure 2.10

### Implementing AND Using only NOR Gates

An AND gate can be replaced by NOR gates as shown in the figure (The AND gate is replaced by a NOR gate with all its inputs complemented by NOR gate inverters)

Figure 2.11

Thus, the NOR gate is a universal gate since it can implement the AND, OR and NOT functions.

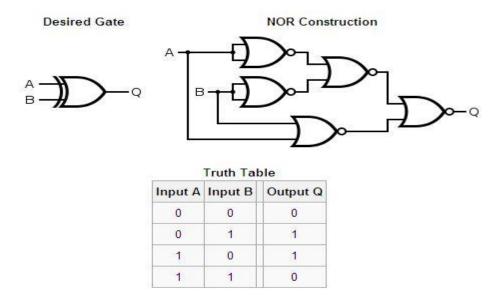

### **Implementing EX-NOR Using only NOR Gates**

Figure 2.12

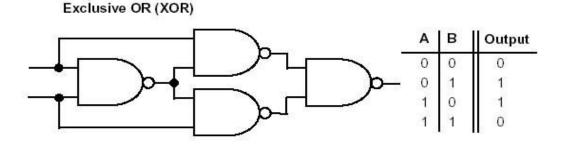

### **Implementing EXOR Using only NOR Gates**

Figure 2.13: Logic Diagram & truth table of XOR gate

### **Implementing NAND Using only NOR Gates**

Figure 2.14

### **Procedure:**

- Test the digital ICs (7400, 7402) with the help of IC tester.

- Make the connections on breadboard as per the pin diagram. Connect the inputs of the logic gate to the logic sources and its output to the logic indicator.

- Apply various input combinations and observe output for each one.

- Verify the truth table for each input/ output combination.

<u>Output:</u> The truth tables of logic gates: AND, OR, NOT, NAND, NOR Ex-OR and Ex-NOR are verified using the universal gate ICs 7400 and IC 7402.

<u>Result</u>: The universal gates are the gates which can implement any Boolean function without need to use any other gate type. Hence all the gates are realized using Universal gates. In practice, this is advantageous since NAND and NOR gates are economical and easier to fabricate and are the mostly used gates in digital logic families.

### **Discussion:**

- Q1. Why NAND & NOR gates are called universal gates?

- Q2. Which gate is equal to AND-inverter Gate?

- Q3. Which gate is equal to OR-inverter Gate?

- Q4. Draw X = ab + b'a' by NAND gate?

- Q5. What is Demorgan's theorem?

- Q6. Solve following example by Demorgan's theorem

### Experiment No. -3

**<u>Aim:</u>** To realize SOP and POS expressions.

<u>Apparatus / Component Required:</u> IC tester, Digital trainer kit, Digital ICs (7400, 7402, 7408, 7432).

### Theory:

#### **Sum of Product (SOP)**

The sum-of-products (SOP) form is a method (or form) of simplifying the Boolean expressions of logic gates. In this SOP form of Boolean function representation, the variables are operated by AND (product) to form a product term and all these product terms are ORed (summed or added) together to get the final function. A sum-of-products form can be formed by adding (or summing) two or more product terms using a Boolean addition operation. Here the product terms are defined by using the AND operation and the sum term is defined by using OR operation.

The sum-of-products form is also called as Disjunctive Normal Form as the product terms are ORed together and Disjunction operation is logical OR. Sum-of-products form is also called as Standard SOP.

SOP form representation is most suitable to use them in FPGA (Field Programmable Gate Arrays).

### **Product of Sums (POS)**

The product of sums form is a method (or form) of simplifying the Boolean expressions of logic gates. In this POS form, all the variables are ORed, i.e. written as sums to form sum terms. All these sum terms are ANDed (multiplied) together to get the product-of-sum form. This form is exactly opposite to the SOP form. So this can also be said as "Dual of SOP form".

Here the sum terms are defined by using the OR operation and the product term is defined by using AND operation. When two or more sum terms are multiplied by a Boolean OR operation, the resultant output expression will be in the form of product-of-sums form or POS form.

The product-of-sums form is also called as Conjunctive Normal Form as the sum terms are ANDed together and Conjunction operation is logical AND. Product-of-sums form is also called as Standard POS.

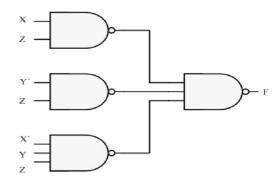

#### **Implement the following SOP function**

$$\mathbf{F} = XZ + \overline{Y}Z + \overline{X}YZ$$

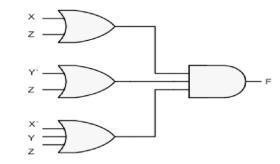

Being an SOP expression, it is implemented in 2-levels as shown in the figure. Here the expression is realized using NAND Gate.

Figure 3.1: SOP using NAND gate

Implement the following POS function

$$\mathbf{F} = (X+Z)(\overline{Y}+Z)(\overline{X}+Y+Z)$$

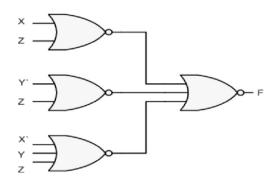

Being a POS expression, it is implemented in 2-levels as shown in the figure.

Figure 3.2: POS using OR & AND gate

Introducing two successive inverters at the inputs of the AND gate Results in the shown equivalent implementation. Since two successive inverters on the same line will not have an overall effect on the logic as it is shown before.

Figure 3.3: POS using NOR gate

#### **Procedure:**

- Test the digital ICs with the help of IC tester.

- Make the connections on the breadboard as per the pin diagram and circuit. Connect the inputs of the logic gate to the logic sources and its output to the logic indicator.

- Apply various input combinations and observe output for each one.

- Verify the circuit for each input/ output combination.

<u>Output:</u> We have implemented the given Boolean function using logic gates in both SOP and POS forms.

**Result:** In the experiment, De-Morgan's theorem and postulate of Boolean algebra are verified. Also the Sum of products and product of sum expressions are realized using the basic gates and the universal gates.

#### **Discussion:**

- Q1. Express the function f(x, y, z) = 1 in the form of sum of minterms and a product of maxterms.

- Q2. What is D'morgans theorem?

- Q3. Solve following example by using D'morgans theorem.

Q4. Examine this truth table and then write both SOP and POS Boolean expressions describing the Output:

| A | В | С | output |

|---|---|---|--------|

| 0 | 0 | 0 | 1      |

| 0 | 0 | 1 | 0      |

| 0 | 1 | 0 | 1      |

| 0 | 1 | 1 | 0      |

| 1 | 0 | 0 | 0      |

| 1 | 0 | 1 | 1      |

| 1 | 1 | 0 | 1      |

| 1 | 1 | 1 | 0      |

Q5. Convert the following SOP expression to an equivalent POS expression.

$$ABC + A\overline{B}\overline{C} + A\overline{B}C + AB\overline{C} + \overline{A}\overline{B}C$$

- Q6. Express the function f(x, y, z) = 1 in the sum of minterms and a product of maxterms? Minterms = (0,1,2,3,4,5,6,7), Maxterms = No maxterms.

- Q7. Make the truth table of  $\pi$ M(1,2,6,7,13,14,15) + d(0,3,5)?

### **Experiment No: 4**

<u>Aim:</u> To realize half adder/ Subtractor & Full Adder/ Subtractor using NAND & NOR gates and to verify their truth table.

Apparatus/ Component Required: IC tester, Digital trainer kit, Digital ICs (7400, 7402)

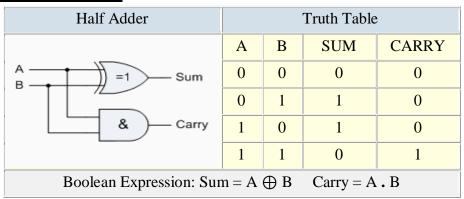

<u>Theory:</u> A very useful combinational logic circuit which can be constructed using just a few basic logic gates and adds together binary numbers is the **Binary Adder** circuit. The Binary Adder is made up from standard AND and Ex-OR gates and allow us to "add" together single bit binary numbers, a and b to produce two outputs, the SUM of the addition and a CARRY called the Carry-out, ( **Cout** ) bit. One of the main uses for the **Binary Adder** is in arithmetic and counting circuits.

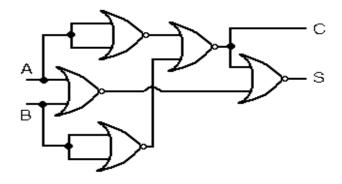

# The Half Adder Circuit 1-bit Adder with Carry-Out

Figure 4.1: Logic diagram & truth table of half adder

From the truth table we can see that the SUM (S) output is the Result of the Ex-OR gate and the Carry-out (Cout) is the Result of the AND gate. One major disadvantage of the Half Adder circuit when used as a binary adder, is that there is no provision for a "Carry-in" from the previous circuit when adding together multiple data bits. For example, suppose we want to add together two 8-bit bytes of data, any Resulting carry bit would need to be able to "ripple" or move across the bit patterns starting from the least significant bit (LSB).

Figure 4.2: Circuit diagram for half-adder using NAND gates

Figure 4.3: Circuit diagram for half-adder using NOR gates

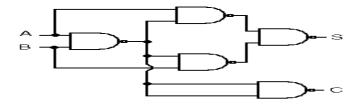

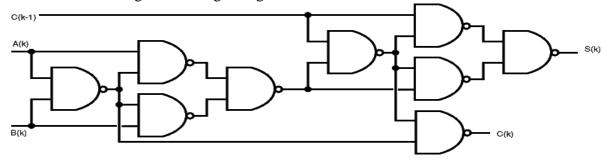

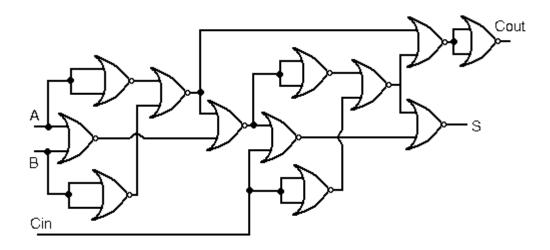

<u>The Full Adder Circuit:</u> The main difference between the Full Adder and the previous seen Half Adder is that a full adder has three inputs, the same two single bit binary inputs A and B as before plus an additional *Carry-In* (C-in) input as shown below. The 1-bit Full Adder circuit above is basically two half adders connected together and consists of three Ex-OR gates, two AND gates and an OR gate, six logic gates in total.

| Full Adder Truth Table                               |   |   |      |     |       |

|------------------------------------------------------|---|---|------|-----|-------|

|                                                      | A | В | C-in | Sum | C-out |

| A B =1 Sum                                           | 0 | 0 | 0    | 0   | 0     |

|                                                      | 0 | 1 | 0    | 1   | 0     |

|                                                      | 1 | 0 | 0    | 1   | 0     |

|                                                      | 1 | 1 | 0    | 0   | 1     |

| ≥1 —C-out                                            | 0 | 0 | 1    | 1   | 0     |

| &                                                    | 0 | 1 | 1    | 0   | 1     |

|                                                      | 1 | 0 | 1    | 0   | 1     |

|                                                      |   | 1 | 1    | 1   | 1     |

| Boolean Expression: Sum = A $\oplus$ B $\oplus$ C-in |   |   |      |     |       |

Figure 4.4: Logic diagram & truth table of half adder

Figure 4.5: Full Adder implementation using NAND Gate

Figure 4.6: Full Adder implementation using NOR Gate

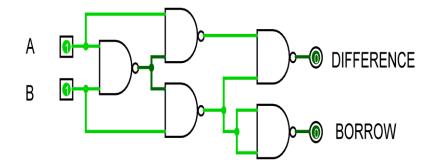

### **The Half Subtractor Circuit**

A half-subtractor has two inputs and two outputs. Let the input variables minuend and subtrahend be designated as A and B respectively, and output functions be designated as DIFF for difference and BORROW for borrow. The truth table of the functions is as follows.

| Half Subtractor                                        | Truth Table |   |      |        |  |  |

|--------------------------------------------------------|-------------|---|------|--------|--|--|

|                                                        | A           | В | DIFF | BORROW |  |  |

| A B DIFF                                               |             | 0 | 0    | 0      |  |  |

|                                                        |             | 1 | 1    | 1      |  |  |

| BORROW                                                 | 1           | 0 | 0    | 1      |  |  |

|                                                        | 1           | 1 | 0    | 0      |  |  |

| Boolean Expression: DIFF = $A \oplus B$ BORROW = A'. B |             |   |      |        |  |  |

Figure 4.7: Circuit diagram & truth table of half subtractor

Figure 4.8: Circuit diagram for half-Subtractor using NAND gates.

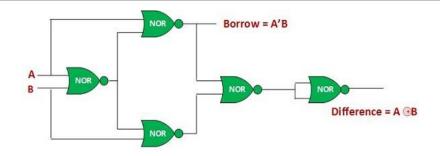

Figure 4.9: Circuit diagram for half-Subtractor using NOR gates.

### **The Full Subtractor Circuit**

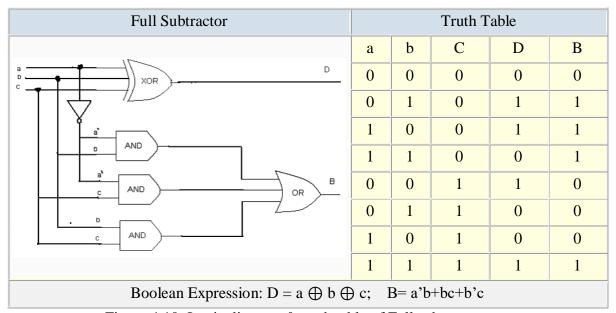

A combinational circuit of full-Subtractor performs the operation of subtraction of three bits—the minuend, subtrahend, and borrow generated from the subtraction operation of previous significant digits and produces the outputs difference and borrow. Let us designate the input variables minuend as A, subtrahend as B, and previous borrow as C, and outputs difference as D and B as Borrow. Eight different input combinations are possible for three input variables.

Figure 4.10: Logic diagram & truth table of Full subtractor

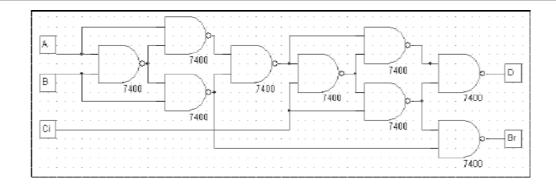

Figure 4.11: Full Subtractor implementation using NAND Gate

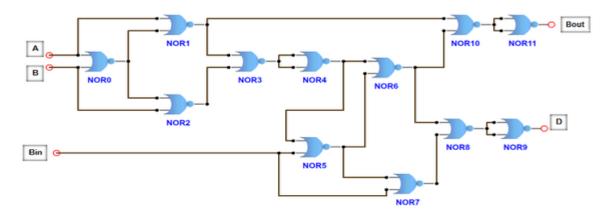

Figure 4.12: Full Subtractor implementation using NOR Gate

### **Procedure:**

- 1. Insert the IC chips into the breadboard. Point all the chips in the same direction with pin 1 at the upper-left corner. (Pin 1 is often identified by a dot or a notch next to it on the chip package).

- 2. Connect +5V and GND pins of each IC chips to the power and ground bus strips on the breadboard.

- 3. Make the connections as per the circuit diagram.

- 4. Switch on V<sub>CC</sub> and apply various combinations of input according to truth table.

- 5. Note down the output readings for half/full adder and sum and the carry bit for different combinations of inputs. Where 5V indicating logic 1 and 0V indicating logic 0.

<u>Output</u>: The truth table for Half adder/Subtractor and Full Adder/Subtractor has been verified.

**Result:** By using various logic gate ICs we can design full or half adder and subtractor. Half adders/subtractors perform their operation on two bits and gives a two bit output. Full adder/subtractor perform their operation on three bit inputs and gives a two bit output.

### **Discussion:**

- Q1. Define Combinational Circuits.

- Q2. What is the difference between half adder and a full adder?

- Q3. What is meant by two and three variable map?

- Q4. Realize half -subtractor and full-subtractor using NOR gates.

- Q5. Realize a full adder using two half adders.

- Q6. Realize a full subtractors using two half subtractors.

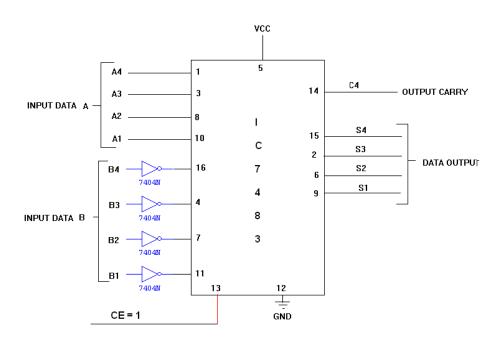

### **Experiment No: 5**

<u>Aim:</u> To design 4-to-1 multiplexer using basic gates and verify the truth table. Also verify the truth table of 8-to-1 multiplexer using IC.

<u>Apparatus / Component Required:</u> IC tester, Digital trainer kit, Digital ICs (74153, 74151, 7408, 7432, 7404, 7411)

#### **Theory:**

#### **MULTIPLEXER:**

Combinational logic switching devices that operate like a very fast acting multiple position rotary A data selector, more commonly called a Multiplexer, shortened to "Mux" or "MPX", are switch. They connect or control, multiple input lines called "channels" consisting of 2, 4, 8 or 16 individual inputs, one at a time to an output. Then the job of a multiplexer is to allow multiple signals to share a single common output.

Multiplexer means transmitting a large number of information units over a smaller number of channels or lines. A digital multiplexer is a combinational circuit that selects binary information from one of many input lines and directs it to a single output line. The selection of a particular input line is controlled by a set of selection lines. Normally there are 2n input line and n selection lines whose bit combination determine which input is selected.

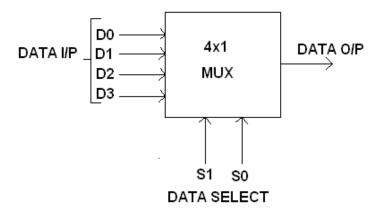

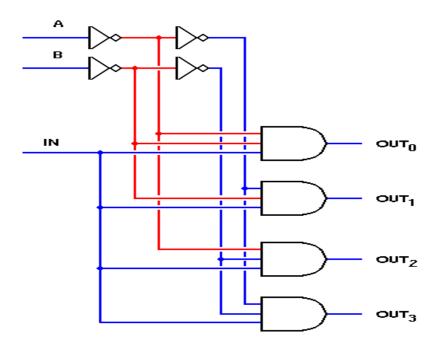

#### **BLOCK DIAGRAM FOR 4:1 MULTIPLEXER:**

Figure 5.1

## **TRUTH TABLE:**

| S1 | $\mathbf{S0}$ | Y = OUTPUT |

|----|---------------|------------|

| 0  | 0             | <b>D</b> 0 |

| 0  | 1             | <b>D1</b>  |

| 1  | 0             | <b>D2</b>  |

| 1  | 1             | D3         |

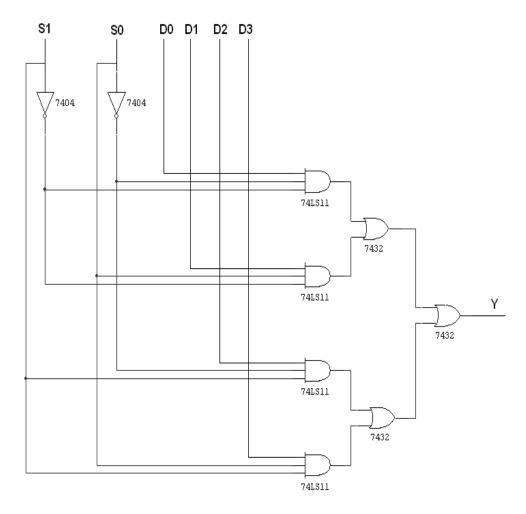

# CIRCUIT DIAGRAM FOR MULTIPLEXER:

Figure 5.2

## **FUNCTION TABLE:**

| <b>S1</b> | S0 | INPUT                          |

|-----------|----|--------------------------------|

| 0         | 0  | $X \rightarrow D0 = X S1' S0'$ |

| 0         | 1  | $X \rightarrow D1 = X S1' S0$  |

| 1         | 0  | $X \rightarrow D2 = X S1 S0$   |

| 1         | 1  | $X \rightarrow D3 = X S1 S0$   |

Y = X S1' S0' + X S1' S0 + X S1 S0' + X S1 S0

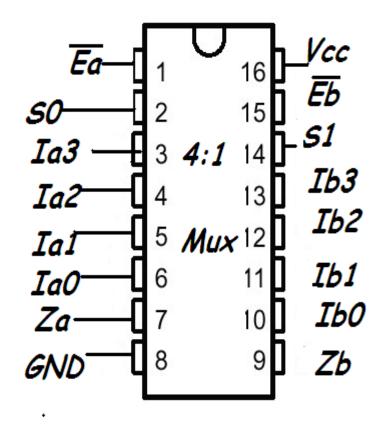

## **PIN DIAGRAM FOR IC 74153**

Figure 5.3

TRUTH TABLE OF 4:1 MUX(IC 74153) (CHANNEL A) WITH ACTIVE LOW MODE:

|                | Inpu     | ts(Chai         | nnel A)  | Selec    | et lines | Output |                           |

|----------------|----------|-----------------|----------|----------|----------|--------|---------------------------|

| $\mathbf{E_a}$ | $I_{ao}$ | I <sub>a1</sub> | $I_{a2}$ | $I_{a3}$ | $S_0$    | $S_1$  | $\mathbf{Z}_{\mathbf{a}}$ |

| 1              | ×        | ×               | ×        | ×        | ×        | ×      | 0                         |

| 0              | 0        | ×               | ×        | ×        | 0        | 0      | 0                         |

| 0              | 1        | ×               | ×        | ×        | 0        | 0      | 1                         |

| 0              | ×        | 0               | ×        | ×        | 0        | 1      | 0                         |

| 0              | ×        | 1               | ×        | ×        | 0        | 1      | 1                         |

| 0              | ×        | ×               | 0        | ×        | 1        | 0      | 0                         |

| 0              | ×        | ×               | 1        | ×        | 1        | 0      | 1                         |

| 0              | ×        | ×               | ×        | 0        | 1        | 1      | 0                         |

| 0              | ×        | ×               | ×        | 1        | 1        | 1      | 1                         |

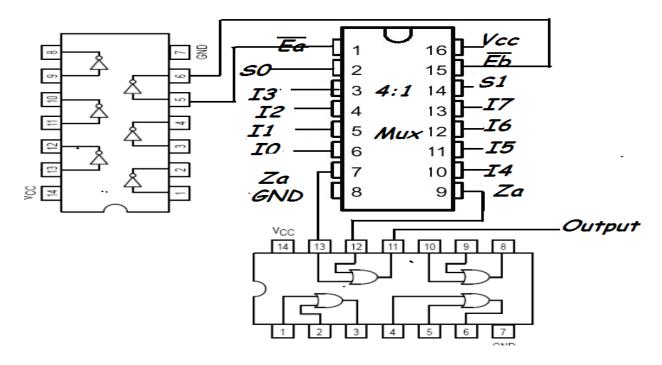

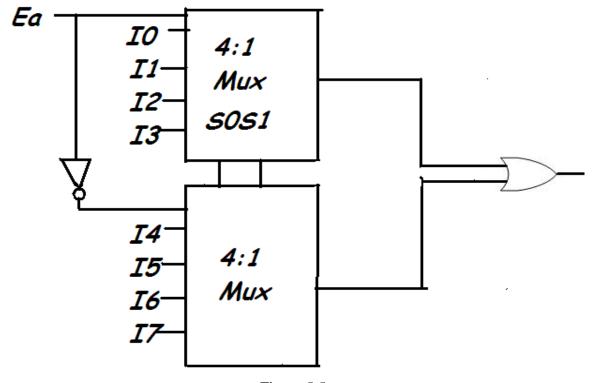

### **IMPLEMENTATION OF 8:1 MULTIPLEXER USING 4:1 MUX:**

Figure 5.4

### **CIRCUIT OF 8:1 MUX USING DUAL 4:1 MUX**

Figure 5.5

## **TRUTH TABLE OF 8:1 MUX**

|   | Inp    | Out | puts   |                |                  |

|---|--------|-----|--------|----------------|------------------|

|   | Select |     | Enable |                |                  |

| С | В      | Α   | ĒN     | Y              | Ÿ                |

| х | х      | x   | 1      | 0              | 1                |

| 0 | 0      | 0   | 0      | D <sub>0</sub> | D <sub>0</sub>   |

| 0 | 0      | 1   | 0      | D <sub>1</sub> | $\bar{D}_1$      |

| 0 | 1      | 0 , | 0      | D <sub>2</sub> | $\overline{D}_2$ |

| 0 | 1      | 1   | 0      | D <sub>3</sub> | $\bar{D}_3$      |

| 1 | 0      | 0   | 0      | D <sub>4</sub> | D <sub>4</sub>   |

| 1 | 0      | 1   | 0      | D <sub>5</sub> | D <sub>5</sub>   |

| 1 | 1      | 0   | 0      | D <sub>6</sub> | D <sub>6</sub>   |

| 1 | 1      | 1   | 0      | D <sub>7</sub> | $\bar{D}_7$      |

Table: 5.1: Truth table of 8:1 MUX

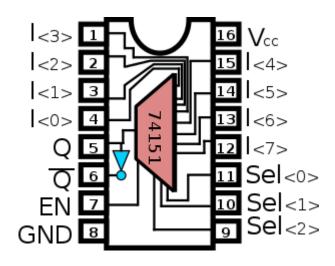

# **IMPLEMENTATION OF 8:1 MULTIPLEXER (74151)**

Figure 5.6

### **Observations for IC 74153**

| Symbol          | Parameter                      | Min  | Nom | Max  | Units |

|-----------------|--------------------------------|------|-----|------|-------|

| V <sub>CC</sub> | Supply Voltage                 | 4.75 | 5   | 5.25 | V     |

| V <sub>IH</sub> | HIGH Level Input Voltage       | 2    |     |      | V     |

| V <sub>IL</sub> | LOW Level Input Voltage        |      |     | 0.8  | V     |

| I <sub>OH</sub> | HIGH Level Output Current      |      |     | -0.4 | mA    |

| I <sub>OL</sub> | LOW Level Output Current       |      |     | 8    | mA    |

| T <sub>A</sub>  | Free Air Operating Temperature | 0    |     | 70   | °C    |

|                 |                                |      |     |      |       |

### **Procedure:**

- 1. Test the digital ICs with the help of IC tester.

- 2. Make the connections as per the circuit diagram.

- 3. Connect the output pin on LED through Resistor.

- 4. Switch on V<sub>CC</sub> and apply various combinations of input according to truth table.

- 5. Observe the logical output and verify with the truth tables.

<u>Output</u>: Hence the 4:1mux is designed with basic gate as given in the figure and verified with the truth table. 8:1 mux are designed with 4:1mux as given in circuit.

**Result:** 4:1 multiplexer and 8:1 multiplexer can be realized using basic logic gates, they can also be designed by using IC 74153 (multiplexer) and IC 74151 (multiplexer).

#### **Discussion:**

- Q1. What is the function of the enable input in a Multiplexer?

- Q2. What is the difference between multiplexer and decoder?

- Q3. List out the applications of multiplexer?

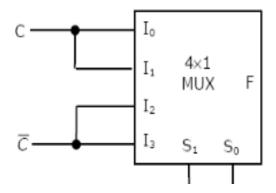

- Q4. Realize the following Boolean expression using 4:1 MUXs only

- $Z = \overline{A}\overline{B}\overline{C}\,\overline{D} + \overline{A}BC\overline{D} + A\overline{B}C\overline{D} + A\overline{B}C\overline{D} + A\overline{B}C\overline{D} + ABCD$

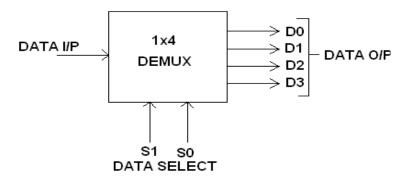

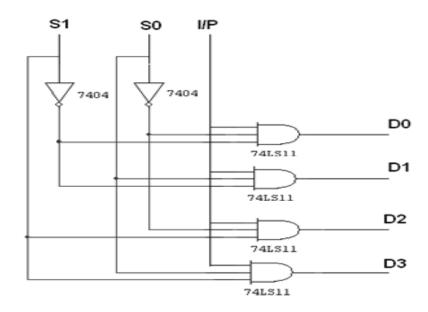

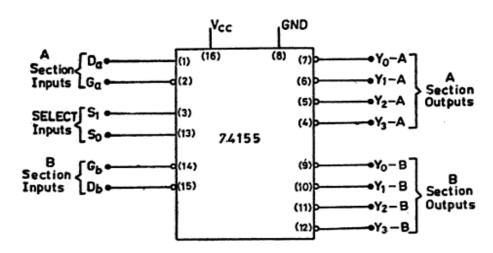

### **Experiment No: 6**

<u>Aim:</u> Design and realize a combinational circuit that will accept the 2421 BCD code and drive a TIL-312 to 7-Segment Display

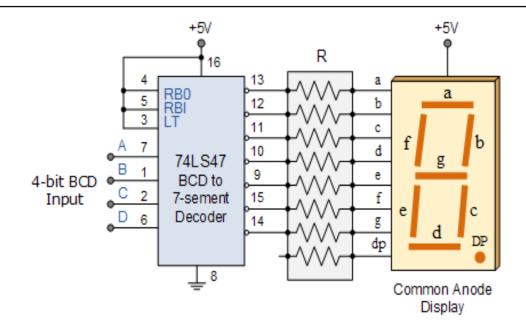

Apparatus / Component Required: IC tester, Digital trainer kit, Digital ICs (7447), register (200  $\Omega$  / 330  $\Omega$ ), seven segment display

#### **Theory:**

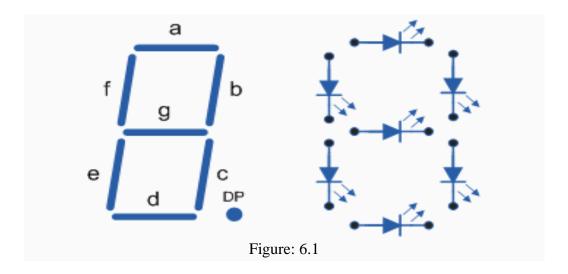

The Binary Coded Decimal (BCD) to 7-Segment Display Decoder. 7-segment **LED** (Light Emitting Diode) or **LCD** (Liquid Crystal) displays, provide a very convenient way of displaying information or digital data in the form of numbers, letters or even alpha-numerical characters and they consist of 7 individual LED's (the segments), within from 0 to 9 and A to F respectively, on the display the correct combination of LED segments need to be illuminated and **BCD** to **7-segment Display Decoders** such as the 74LS47 do just that. A standard 7-segment LED display generally has 8 input connections, one for each LED segment and one that acts as a common terminal or connection for all the internal segments. There are two important types of 7-segment LED digital display.

- The Common Cathode Display (CCD) In the common cathode display, all the cathode connections of the LED's are joined together to logic "0" and the individual segments are illuminated by application of a "HIGH", logic "1" signal to the individual Anode terminals.

- The Common Anode Display (CAD) In the common anode display, all the anode connections of the LED's are joined together to logic "1" and the individual segments are illuminated by connecting the individual Cathode terminals to a "LOW", logic "0" signal.

#### 7-Segment Display Format

Figure: 6.2: 7-Segment Display Elements for all Numbers.

It can be seen that to display any single digit number from 0 to 9 or letter from A to F, we would need 7 separate segment connections plus one additional connection for the LED's "common" connection. Also as the segments are basically a standard light emitting diode, the driving circuit would need to produce up to 20mA of current to illuminate each individual segment and to display the number 8, all 7 segments would need to be lit resulting a total current of nearly 140mA, (8 x 20mA). Obviously, the use of so many connections and power consumption is impractical for some electronic or microprocessor based circuits and so in order to reduce the number of signal lines required to drive just one single display, display decoders such as the BCD to 7-Segment Display Decoder and Driver IC's are used instead.

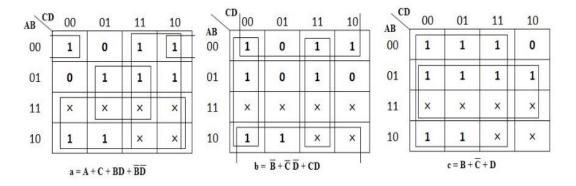

#### Combinational circuit for converting 2421 BCD code to seven segment number

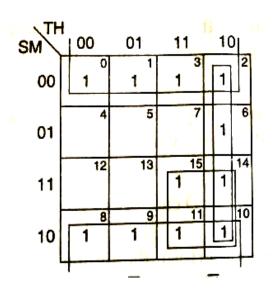

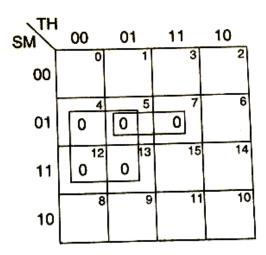

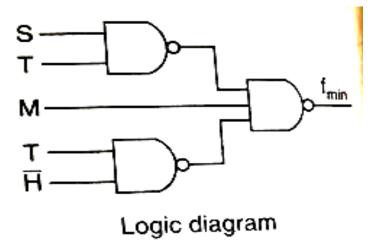

Both the 2421 code and BCD code are 4-bit codes and represent the decimal equivalents 0 to 9. To design the converter circuit for the above, first the truth table is prepared with the input variables W, X, Y, and Z of 2421 code, and the output variables A, B, C, and D. Karnaugh maps to obtain the simplified expressions of the output functions are shown in Figure. Unused combinations are considered as don't-care condition.

| Decimal | - Ir | put | line | s |   | Output lines |   |   |   |   | Display |         |

|---------|------|-----|------|---|---|--------------|---|---|---|---|---------|---------|

| Digit   | Α    | В   | С    | D | а | b            | С | d | е | f | g       | pattern |

| 0       | 0    | 0   | 0    | 0 | 1 | 1            | 1 | 1 | 1 | 1 | 0       | 8       |

| 1       | 0    | 0   | 0    | 1 | 0 | 1            | 1 | 0 | 0 | 0 | 0       | 8       |

| 2       | 0    | 0   | 1    | 0 | 1 | 1            | 0 | 1 | 1 | 0 | 1       | 8       |

| 3       | 0    | 0   | 1    | 1 | 1 | 1            | 1 | 1 | 0 | 0 | 1       | 8       |

| 4       | 0    | 1   | 0    | 0 | 0 | 1            | 1 | 0 | 0 | 1 | 1       | 8       |

| 5       | 0    | 1   | 0    | 1 | 1 | 0            | 1 | 1 | 0 | 1 | 1       | 8       |

| 6       | 0    | 1   | 1    | 0 | 1 | 0            | 1 | 1 | 1 | 1 | 1       | 8       |

| 7       | 0    | 1   | 1    | 1 | 1 | 1            | 1 | 0 | 0 | 0 | 0       | - 8     |

| 8       | 1    | 0   | 0    | 0 | 1 | 1            | 1 | 1 | 1 | 1 | 1       | 8       |

| 9       | 1    | 0   | 0    | 1 | 1 | 1            | 1 | 1 | 0 | 1 | 1       | 8       |

Table 6.1: Truth Table for BCD to Seven Segment

### **Decoder**

## The output expressions are:

$$a = F1 (A, B, C, D) = \sum m (0, 2, 3, 5, 7, 8, 9)$$

$$b = F2 (A, B, C, D) = \sum m (0, 1, 2, 3, 4, 7, 8, 9)$$

$$c = F3 (A, B, C, D) = \sum m (0, 1, 3, 4, 5, 6, 7, 8, 9)$$

$$d = F4 (A, B, C, D) = \sum m (0, 2, 3, 5, 6, 8)$$

$$e = F5 (A, B, C, D) = \sum m (0, 2, 6, 8)$$

$$f = F6 (A, B, C, D) = \sum m (0, 4, 5, 6, 8, 9)$$

$$g = F7 (A, B, C, D) = \sum m (2, 3, 4, 5, 6, 8, 9)$$

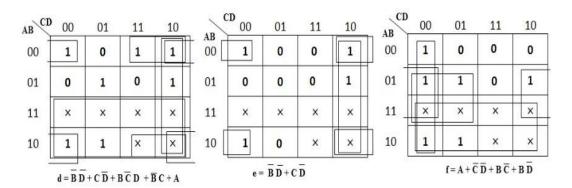

The K-Map of the above expressions are:

Figure: 6.3

| AB CI                                                                                                                                                                 | 00 | 01 | 11 | 10 |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|----|----|----|--|--|

| 00                                                                                                                                                                    | 0  | 0  | 1  | 1  |  |  |

| 01                                                                                                                                                                    | 1  | 1  | 0  | 1  |  |  |

| 11                                                                                                                                                                    | ×  | ×  | ×  | ×  |  |  |

| 10                                                                                                                                                                    | 1  | 1  | ×  | ×  |  |  |

| $\mathbf{g} = \overline{\mathbf{B}} \mathbf{C} + \mathbf{C} \overline{\mathbf{D}} + \mathbf{B} \overline{\mathbf{C}} + \mathbf{B} \overline{\mathbf{C}} + \mathbf{A}$ |    |    |    |    |  |  |

Figure: 6.4

From the above simplification, we get the output values as

$$a = A + C + BD + \overline{B} \overline{D}$$

$$b = \overline{B} + \overline{C} \overline{D} + CD$$

$$c = B + \overline{C} + D$$

$$d = \overline{B} \overline{D} + C \overline{D} + B \overline{C} D + \overline{B} C + A$$

$$e = \overline{B} \overline{D} + C \overline{D}$$

$$f = A + \overline{C} \overline{D} + B \overline{C} + B \overline{D}$$

$$g = A + B \overline{C} + \overline{B} C + C \overline{D}$$

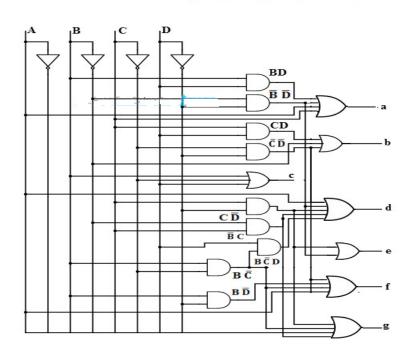

Figure 6.5: Logic diagram of BCD to Seven segment decoder

### **Procedure:**

- 1. Test the digital ICs with the help of IC tester.

- 2. Make the connections as per the circuit diagram on the digital trainer kit.

- 3. Connect the output pins to the seven segment pins.

- 4. Switch on V<sub>CC</sub> and apply various combinations of input according to the truth table.

- 5. Observe the logical output and verify with the truth tables.

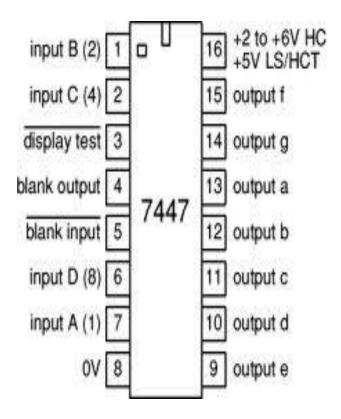

#### BCD to 7-Segment Display Decoders using TTL 74LS47

A binary coded decimal (BCD) to 7-segment display decoder such as the TTL 74LS47 or 74LS48, have 4 BCD inputs and 7 output lines, one for each LED segment. This allows a smaller 4-bit binary number (half a byte) to be used to display all the denary numbers from 0 to 9 and by adding two displays together, a full range of numbers from 00 to 99 can be displayed with just a single byte of 8 data bits.

## PIN diagram for 7447 IC:

Figure 6.6: PIN diagram for 7447 IC

The use of **packed** BCD allows two BCD digits to be stored within a single byte (8-bits) of data, allowing a single data byte to hold a BCD number in the range of 00 to 99.

Fiure 6.7:.4 BCD to 7-Segment Display Decoders using TTL 74LS47

# **Observations:** For DM7447A:

| Symbol            | Parameter                         | Min  | Typical | Max  | Unit |

|-------------------|-----------------------------------|------|---------|------|------|

| Vcc               | Supply Voltage                    | 4.75 | 5       | 5.25 | V    |

| $V_{\mathrm{IH}}$ | High Level Input Voltage          | 2    | -       | -    | V    |

| $V_{\rm IL}$      | Low Level Input Voltage           | -    | -       | 0.8  | V    |

| V <sub>OH</sub>   | High level output voltage(a to g) | -    | -       | 30   |      |

| Іон               | High Level Output Current(BI/RBO) | -    | -       | -0.2 | μА   |

| I <sub>OL</sub>   | Low Level Output Current(a to g)  | -    | -       | 40   | mA   |

<u>Output</u>: Hence the BCD to seven segment display is designed using basic gates and with a BCD to seven segment display IC as given in the figure and verified with the truth table.

**Result:** It is possible to display any single digit number on a 7-segment display by sending a high digital signal to the specific segments that make up the number. It is possible to display the decimal value of a binary number on a 7-segment display using a BCD decoder. However, this method will allow displaying only digits from 0 to 9. In the case of the decoder circuit, any binary number between 1010 through 1111 (A to F) is an invalid input and would provide distorted shapes on the LCD display. The usage of a 7-segment display paired with a BCD decoder is opening the door for an application using digital computation requiring a human-readable. That application can be for instance: "a clock, a timer, a calculator, counter..." Thus we had concluded that 7 segment display can be implemented using IC,s and we had seen different numbers 0-9.

#### **Discussion:**

- Q1. What is code conversion?

- Q2. Can a decoder function as a Demultiplexer?

- Q3. Give the applications of seven segment display?

- Q4. What are happened if the input given in between A to F.

### **Experiment No: 7**

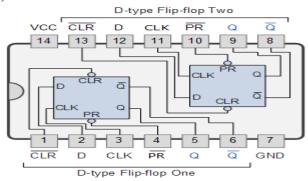

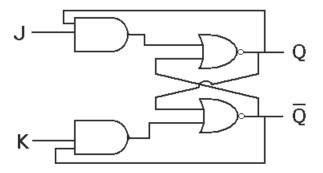

<u>Aim:</u> Using basic logic gates realize the R-S, J-K and D flip flops with and without clock pulse and verify truth table.

<u>Apparatus / Component Required:</u> IC tester, Digital trainer kit, connecting wires, Digital ICs (7400, 7402, 7404, 7408, 7432)

#### Theory:

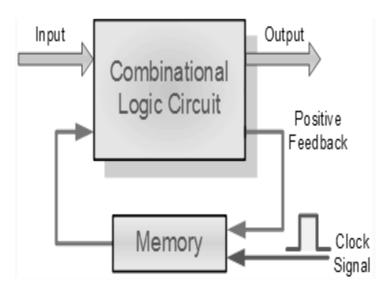

Sequential Logic circuits have some form of inherent "Memory" built in to them as they are able to take into account their previous input state as well as those actually present, a sort of "before" and "after" is involved with sequential circuits.

In other words, the output state of a sequential logic circuit is a function of the following three states, the "present input", the "past input" and/or the "past output". Sequential Logic circuits remember these conditions and stay fixed in their current state until the next clock signal changes one of the states, giving sequential logic circuits "Memory".

Sequential logic circuits are generally termed as two state or <u>Bistable</u> devices which can have their output or outputs set in one of two basic states, a logic level "1" or a logic level "0" and will remain "latched" (hence the name latch) indefinitely in this current state or condition until some other input trigger pulse or signal is applied which will cause the bistable to change its state once again.

### **Sequential Logic Representation**

Figure 7.1: Block diagram of Sequential circuit

The word "Sequential" means that things happen in a "sequence", one after another and in Sequential Logic circuits, the actual clock signal determines when things will happen next.

Simple sequential logic circuits can be constructed from standard Bistable circuits such as Flip-flops, Latches and Counters and which themselves can be made by simply connecting together universal NAND Gates and/or NOR Gates in a particular combinational way to produce the required sequential circuit.

#### FLIP-FLOP:-

"Flip-flop" is the common name given to two-state devices which offer basic memory for sequential logic operations. Flip-flops are heavily used for digital data storage and transfer and are commonly used in banks called "register" for the storage of binary numerical data.

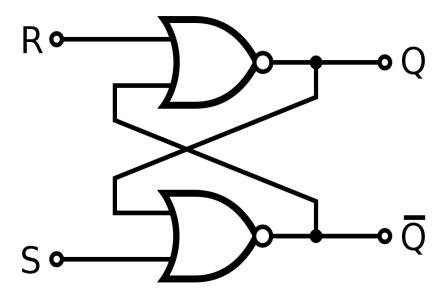

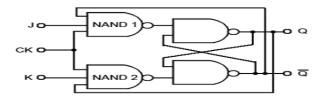

#### S-R Flip Flop

The SR flip-flop can be considered as a 1-bit memory, since it stores the input pulse even after it has passed. Flip-flops (or bi-stables) of different types can be made from logic gates and, as with other combinations of logic gates, the NAND and NOR gates are the most versatile, the NAND being most widely used. This is because, as well as being universal, i.e. it can be made to mimic any of the other standard logic functions, it is also cheaper to construct. The SET-RESET flip flop is designed with the help of two NOR gates and also two NAND gates. These flip flops are also called S-R Latch.

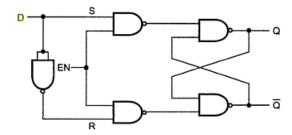

### • S-R Filp Flop using NOR Gate(Without Clock)

The design of such a flip flop includes two inputs, called the SET [S] and RESET [R]. There are also two outputs, Q and Q'. The diagram and truth table is shown below.

Figure 7.2: Logic Diagram of NOR based S-R Flip flop

| Inputs |   | Out       | Action               |           |

|--------|---|-----------|----------------------|-----------|

| S      | R | $Q_{n+1}$ | $\overline{Q_{n+1}}$ |           |

| 0      | 0 | Qn        | $\overline{Q_n}$     | No change |

| 0      | 1 | 0         | 1                    | Reset     |

| 1      | 0 | 1         | 0                    | Set       |

| 1      | 1 | ?         | ?                    | Forbidden |

Truth Table – 7.1: S-R Latch using NOR Gate

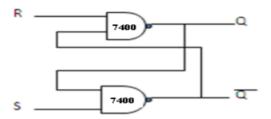

## S-R Flip Flop using NAND Gate(Without Clock)

The circuit of the S-R flip flop using NAND Gate and its truth table is shown below.

Figure 7.3: Logic Diagram of NAND based S-R Latch

Truth Table – 7.2: S-R Latch using NAND Gate

| Inputs |   | Out       | Action |  |

|--------|---|-----------|--------|--|

| S      | R | $Q_{n+1}$ | 0,,1   |  |

| Inp | outs | Out              | Outputs              |              |

|-----|------|------------------|----------------------|--------------|

| S   | R    | Q <sub>n+1</sub> | $\overline{Q_{n+1}}$ |              |

| 0   | 0    | ?                | ?                    | Forbidden    |

| 0   | 1    | 1                | 0                    | Set          |

| 1   | 0    | 0                | 1                    | Reset        |

| 1   | 1    | Qn               | $\overline{Q_n}$     | No<br>change |

|     |      |                  |                      | change       |

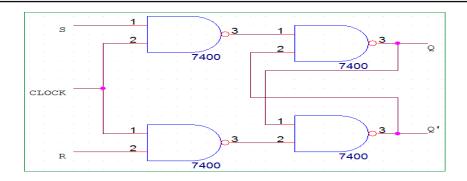

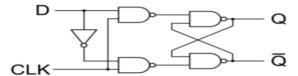

## **Clocked S-R Flip Flop**

It is also called a Gated S-R flip flop.

The problems with S-R flip flops using NOR and NAND gate is the invalid state. This problem can be overcome by using a bistable SR flip-flop that can change outputs when certain invalid states are met, regardless of the condition of either the Set or the Reset inputs. For this, a clocked S-R flip flop is designed by adding two NAND gates to a basic NAND Gate flip flop. The circuit diagram and truth table is shown below.

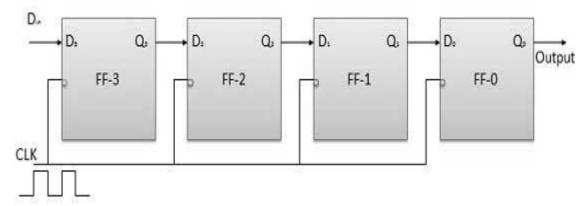

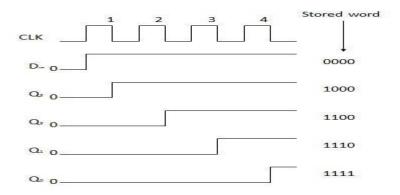

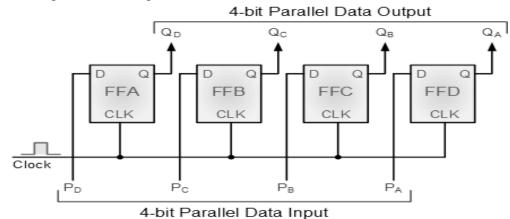

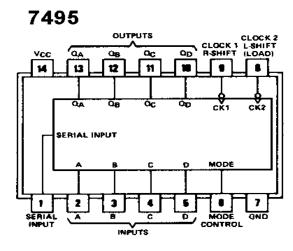

Figure 7.4: Logic Diagram of NAND based Clocked S-R Flip flop